& MOTOROLA INC., 1984

DS9494\_84

Messo

**MOTOROLA** Semiconductor Products Inc.

/ (@ · · · · · ·

| Characteristic                                                                                                                                    |                                                       | Symbol            | Min                                          | Тур   | Max                  | Unit     |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|----------------------------------------------|-------|----------------------|----------|

| Input High Voltage                                                                                                                                |                                                       | VIH               | V <sub>SS</sub> +2.0                         | -     |                      | <u>v</u> |

| Input Low Voltage                                                                                                                                 |                                                       | VIL               | _                                            | -     | V <sub>SS</sub> +0.8 | V        |

|                                                                                                                                                   | , Rx CLK, Rx Data, Enable,<br>, RS, R/W, CS, DCD, CTS | lin               | _                                            | 1.0   | 2.5                  | μA       |

| Hi-Z (Off-State) Input Current<br>(Vin=0.4 to 2.4 V, VCC=5.25 V)                                                                                  | D0-D7                                                 | ΙIZ               |                                              | 2.0   | 10                   | μΑ       |

| Output High Voltage<br>( $I_{Load} = -205 \mu$ A, Enable Pulse Width < 25 $\mu$ s)<br>( $I_{Load} = -100 \mu$ A, Enable Pulse Width < 25 $\mu$ s) | D0-D7<br>TX Data, DTR, TUF                            | V <sub>OH</sub>   | V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4 | -     | B                    | v        |

| Output Low Voltage (ILoad = 1.6 mA, Enable Pulse Wid                                                                                              | th<25 μs)                                             | · V <sub>OL</sub> | —                                            | - Zen | V <sub>SS</sub> +0.4 | <u> </u> |

| Output Leakage Current (Off-State) (VOH = 2.4 V)                                                                                                  | ĪRQ                                                   | loz               | -                                            | 1.0   | 10                   | μA       |

| Internal Power Dissipation (Measured at $T_A = 0^{\circ}C$ )*                                                                                     |                                                       | PINT              |                                              | 300   | 525 *                | mΨ       |

| Input Capacitance<br>(V <sub>in</sub> =0, T <sub>A</sub> =25°C, f=1.0 MHz)                                                                        | D0-D7<br>All Other Inputs                             | C <sub>in</sub>   |                                              |       | 12.5<br>7.5          | pF       |

| Output Capacitance<br>( $V_{in} = 0, T_A = 25^{\circ}C, f = 1.0 \text{ MHz}$ )                                                                    | Tx Data, SM/DTR, TUF                                  | Cout              |                                              | -     | 10<br>5.0            | pF       |

\*For temperatures below 0°C, the maximum value of PINT will increase.

### AC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=5.0 V ±5%, V<sub>SS</sub>=0, T<sub>A</sub>=T<sub>L</sub> to T<sub>H</sub> unless otherwise noted)

|                                                |                     | MC6      |      | MC6   | MC68A52 |       | 8B52  | Unit |

|------------------------------------------------|---------------------|----------|------|-------|---------|-------|-------|------|

| Characteristic                                 | Symbol              | Min      | Max  | Min   | Max     | Min   | Max   |      |

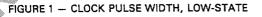

| Serial Clock Pulse Width, Low (Figure 1)       | PWCL                | 700      | -    | 400   | -       | 280   | -     | ns   |

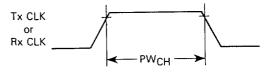

| Serial Clock Pulse Width, High (Figure 2)      | PWCH                | 700      | -    | 400   |         | 280   | -     | ns   |

| Serial Clock Frequency (Rx CLK, Tx CLK)        | fC                  | -        | 600  |       | 1000    | -     | 1500  | kHz  |

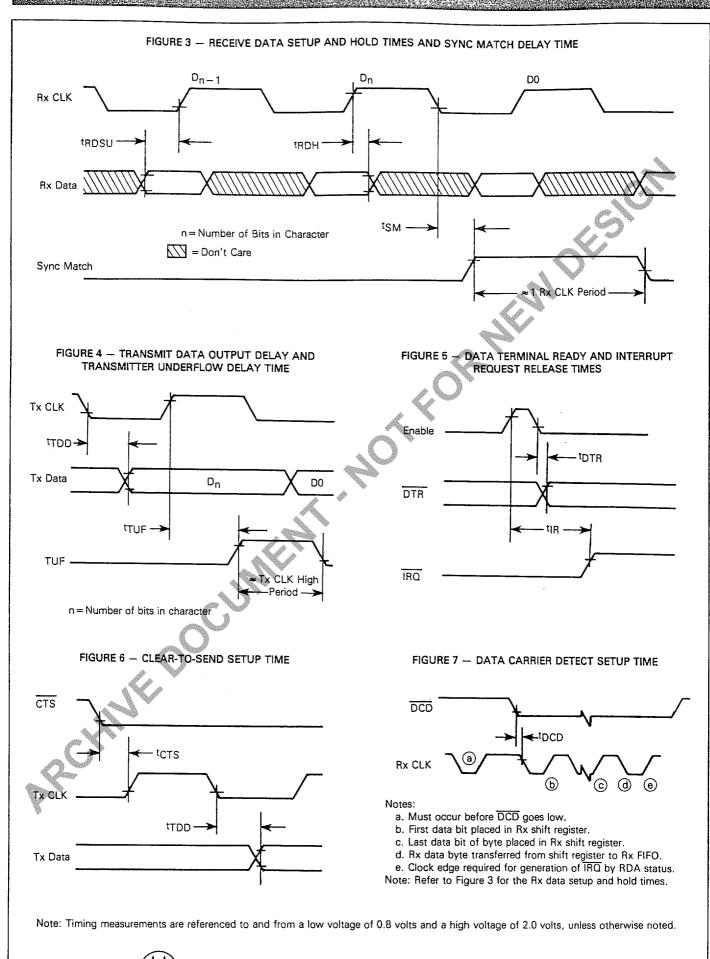

| Receive Data Setup Time (Figure 3, 7)          | <sup>t</sup> RDSU   | 350      | -    | 200   |         | 160   | _     | ns   |

| Receive Data Hold Time (Figure 3)              | <sup>t</sup> RDH    | 350      | -    | 200   |         | 160   | -     | ns   |

| Sync Match Delay Time (Figure 3)               | tsm                 | -        | 1.0  |       | 0.666   | _     | 0.500 | μS   |

| Clock-to-Data Delay for Transmitter (Figure 4) | TDD                 |          | 1.0  | -     | 0.666   | -     | 0.500 | μs   |

| Transmitter Underflow (Figures 4, 6)           | <b>t</b> TUF        | -        | 1.0  |       | 0.666   | -     | 0.500 | μs   |

| DTR Delay Time (Figure 5)                      | <sup>t</sup> DTR    | -        | 1.0  | -     | 0.666   | _     | 0.500 | μs   |

| Interrupt Request Release Time (Figure 5)      | tIR                 | -        | 1.6  |       | 1.1     |       | 0.850 | μS   |

| RESET Pulse Width                              | <sup>t</sup> RESET  | 1.0      | -    | 0.666 | -       | 0.500 | _     | μS   |

| CTS Setup Time (Figure 6)                      | tCTS                | 200      | -    | 150   | -       | 120   |       | ns   |

| DCD Setup Time (Figure 7)                      | tDCD                | 500      | - 1  | 350   | -       | 250   | -     | ns   |

| Input Rise and Fall Times (Except Enable)      | t <sub>r</sub> , tf | <u> </u> | 1.0* |       | 1.0*    |       | 1.0*  | μS   |

\*1.0 µs or 10% of the pulse width, whichever is smaller

## FIGURE 2 - CLOCK PULSE WIDTH, HIGH-STATE

Note: Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

**MOTOROLA** Semiconductor Products Inc. –

##

**NOTOROLA** Semiconductor Products Inc.

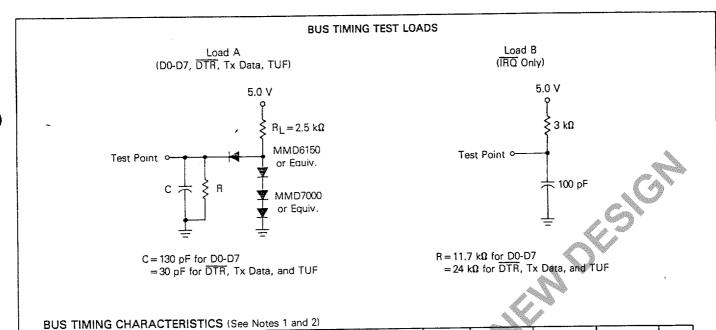

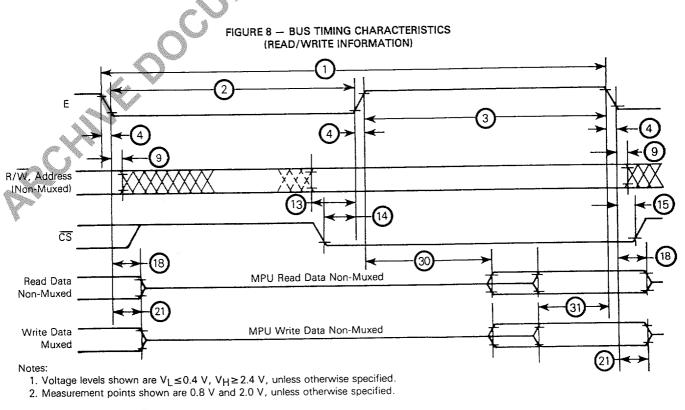

#### MC68B52 MC6852 MC68A52 Unit Indent Symbol Characteristic Min Max Min Max Max Min Number 0.5 10 1.0 10 0.67 10 Cycle Time tcyc 1 210 280 \_ 430 -PWEL Pulse Width, E Low 2 220 280 \_ PWEH 450 \_\_\_\_ -----3 Pulse Width, E High 20 25 25 \_ \_ Clock Rise and Fall Time tr, tr 4 10 10 10 \_ \_ <sup>t</sup>AH -Address Hold Time 9 40 60 80 \_ ---Address Setup Time Before E tAS 13 40 80 ---60 \_ ---tCS 14 Chip Select Setup Time Before E 10 10 \_ 10 ----\_\_\_\_ Chip Select Hold Time <sup>t</sup>CH 15 50\* 30 50\* 50\* 20 20 <sup>t</sup>DHR Read Data Hold Time 18 10 10 <sup>t</sup>DHW 10 \_ 21 Write Data Hold Time 150 180 290 **t**DDR 30 Output Data Delay Time 60 165 80 -\_ Input Data Setup Time tDSW 31

μS

ns

\*The data bus output buffers are no longer sourcing or sinking current by tDHRmax (High Impedance).

**MOTOROLA** Semiconductor Products Inc.

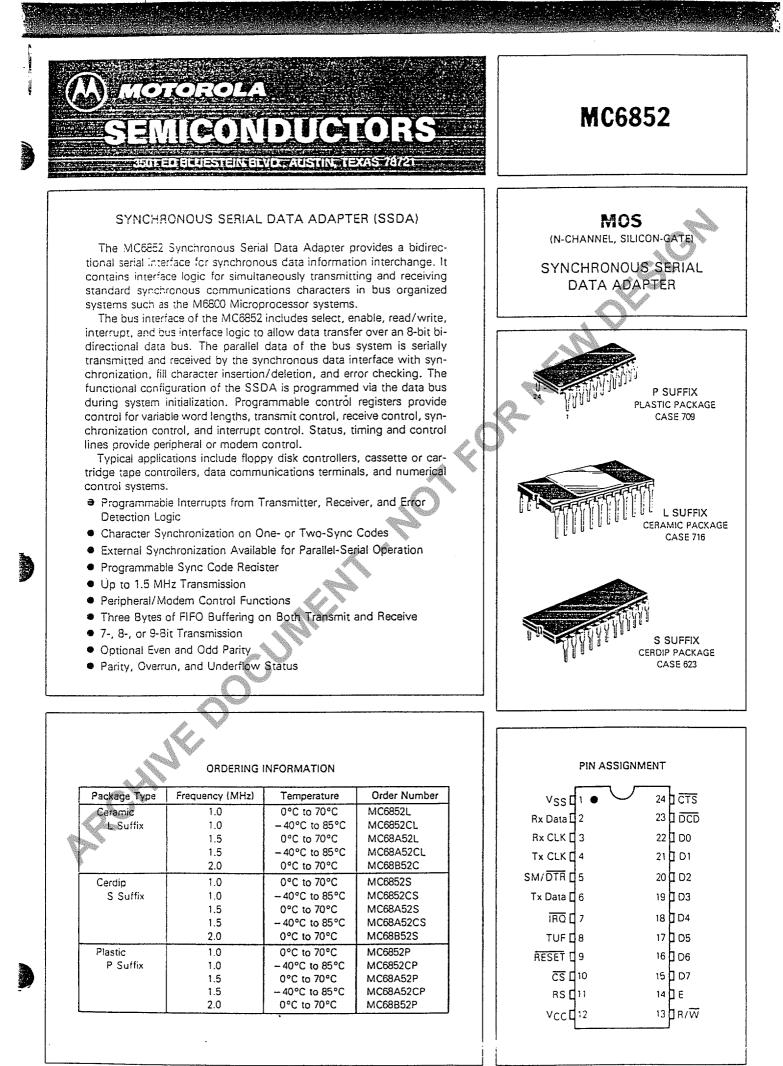

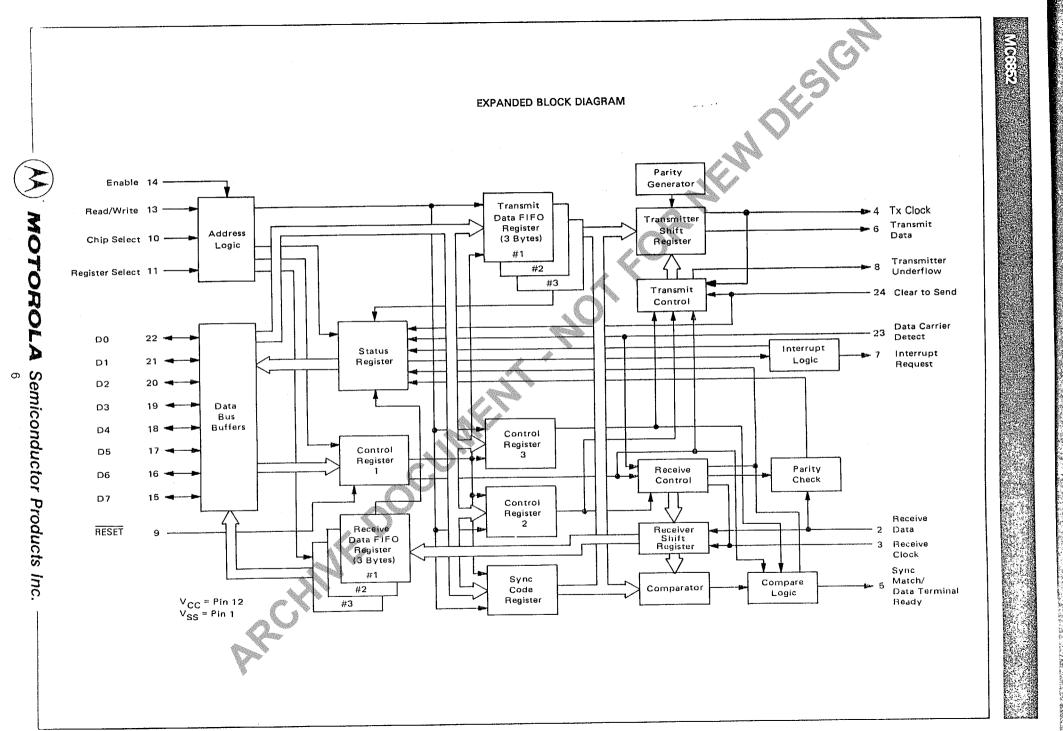

#### **DEVICE OPERATION**

At the bus interface, the SSDA appears as two addressable memory locations. Internally, there are seven registers: two read-only and five write-only registers. The read-only registers are Status and Receive Data; the writeonly registers are Control 1, Control 2, Control 3, Sync Code and Transmit Data. The serial interface consists of serial input and output lines with independent clocks, and four peripheral/modem control lines.

Data to be transmitted is transferred directly into the 3-byte Transmit Data First-In First-Out (FIFO) Register from the data bus. Availability of the input to the FIFO is indicated by the TDRA bit in the Status Register; once data is entered, it moves through the FIFO to the last empty location. Data at the output of the FIFO is automatically transferred from the FIFO to the Transmitter Shift Register as the shift register becomes available to transmit the next character. If data is not available from the FIFO (underflow condition), the Transmitter Shift Register is automatically loaded with either a sync code or an all "1's" character. The transmit seciton may be programmed to append even, odd, or no parity to the transmitted word. An external control line (Clear-to-Send) is provided to inhibit the transmitter without clearing the FIFO.

Serial data is accumulated in the receiver based on the synchronization mode selected. In the external sync mode, used for parallel-serial operation, the receiver is synchronized by the DCD (Data Carrier Detect) input (Figure 9) and transfers successive bytes of data to the input of the Receiver FIFO. The single-sync-character mode requires that a match occur between the Sync Code Register and one incoming character before data transfer to the FIFO begins. The two-sync-character mode requires that two sync codes be received in sequence to establish synchronization. Subsequent to synchronization in any mode, data is accumulated in the shift register, and parity is optionally checked. An indication of parity error is carried through the Receiver FIFO with each character to the last empty location. Availability of a word at the FIFO output is indicated by the RDA status bit in the Status Register, as is a parity error (PE).

The SSDA and its internal registers are selected by RS,  $\overline{CS}$ , Read/Write (R/ $\overline{W}$ ) and Enable control lines. To configure the SSDA, Control Registers are selected and the appropriate bits set. The Status Register is addressable for reading status.

Other I/O lines, in addition to Clear-to-Send (CTS) and Data Carrier Detect (DCD), include SM/DTR (Sync Match/Data Terminal Ready) and Transmitter Underflow (TUF). The transmitter and receiver each have individual clock inputs allowing simultaneous operation under separate clock control. Signals to the microprocessor are the Data Bus and Interrupt Request (IRQ).

#### INITIALIZATION

During a power-on sequence, the SSDA is reset via the RESET input and internally latched in a reset condition to prevent erroneous output transitions. The Receiver Shift Register is set to all "1's". The Sync Code Register, Control Register 2, and Control Register 3 should be programmed prior to the programmed release of the Transmitter and/or Receiver Reset bits; these bits in Control Register 1 should be cleared after the RESET line has gone high.

#### TRANSMITTER OPERATION

Data is transferred to the transmitter section in parallel form by means of the data bus and Transmit Data FIFO. The Transmit Data FIFO is a 3-byte register whose status is indicated by the Transmitter Data Register Available status bit (TDRA) and its associated interrupt enable bit. Data is transferred through the FIFO on negative edges of Enable (E) pulses. Two data transfer modes are provided in the SSDA. The 1-byte transfer mode provides for writing data to the transmitter section (and reading from the receiver section) one byte at a time. The 2-byte transfer mode provides for writing two data characters in succession.

Data will automatically transfer from the last register location in the Transmit Data FIFO (when it contains data) to the Transmitter Shift Register during the last half of the last bit of the previous character. A character is transferred into the Shift Register by the Transmitter Clock. Data is transmitted *LSB first*, and odd or even parity can be optionally appended. The unused bit positions in short word length characters, from the data bus, are "don't cares". (Note: The data bus inputs may be reversed for applications requiring the MSB to be transferred first, e.g., IBM format for floppy disks; however, care must be taken to properly program the control registers — Table 1 will have its bit positions reversed.)

When the Shift Register becomes empty, and data is not available for transfer from the Transmit Data FIFO, an "underflow" occurs, and a character is inserted into the transmitter data stream to maintain character synchronization. The character transmitted on underflow will be either a "Mark" (all "1's") or the contents of the Sync Code Register, depending upon the state of the Transmit Sync Code on Underflow control bit. The underflow condition is indicated by a pulse (=1 Tx CLK high period) on the Underflow output (when in Tx Sync on underflow mode). The Underflow output occurs coincident with the transfer of the last half of the last bit preceding the underflow character. The Underflow status bit is set until cleared by means of the Clear Underflow control bit. This output may be used in floppy disk systems to synchronize write operations and for appending CRCC.

Transmission is initiated by clearing the Transmitter Reset bit in Control Register 1. When the Transmitter Reset bit is cleared, the first *full* positive half-cycle of the Transmit Clock will initiate the transmit cycle, with the transmission of data or underflow characters beginning on the negative edge of the Transmit Clock pulse which started the cycle. If the Transmit Data FIFO was not loaded, an underflow character will be transmitted (see Figure 4).

The Clear-to-Send  $(\overline{CTS})$  input provides for automatic control of the transmitter by means of external system hardware; e.g., the modem  $\overline{CTS}$  output provides the control in a data communications system. The  $\overline{CTS}$  input resets and inhibits the transmitter section when high, but does not reset the Transmit Data FIFO. The TDRA status bit is inhibited by  $\overline{CTS}$  being high in either the one-sync character or two-sync character mode of operation. In the external sync mode, TDRA is unaffected by  $\overline{CTS}$  in order to provide Transmit ter under the control of the  $\overline{CTS}$  input. When the Transmitter Reset bit (Tx Rs) is set, the Transmit Data FIFO is cleared and the TDRA status bit is cleared. After one E clock has occurred, the Transmit Data FIFO becomes available for new data with TDRA inhibited.

#### **RECEIVER OPERATION**

Data and a presynchronized clock are provided to the SSDA receiver section by means of the Receive Data (Rx Data) and Receive Clock (Rx CLK) inputs. The data is a continuous stream of binary data bits without means for identifying character boundaries within the stream. It is, therefore, necessary to achieve character synchronization for the data at the *beginning* of the data block. Once synchronization is achieved, it is assumed to be retained for all successive characters within the block.

Data communications systems utilize the detection of sync codes during the initial portion of the preamble to establish character synchronization. This requires the detection of a single code or two successive sync codes. Floppy disk and cartridge tape units require sixteen bits of defined preamble and cassettes require eight bits of preamble to establish the reference for the start of record. All three are functionally equivalent to the detection of sync codes. Systems which do not utilize code detection techniques require custom logic external to the SSDA for character synchronization and use of the parallel-to-serial (external sync) mode. (Note: The Receiver Shift Register is set to ones when reset.)

#### SYNCHRONIZATION

The SSDA provides three operating modes with respect to character synchronization: one-sync-character mode, twosync-character mode, and external sync mode. The external sync mode requires synchronization and control of the receiving section through the Data Carrier Detect (DCD) input (see Figure 7). This external synchronization could consist of direct line control from the transmitting end of the serial data link or from external logic designed to detect the start of the message block. The one-sync-character mode searches on a bit-by-bit basis until a match is achieved between the data in the Shift Register and the Sync Code Register. The match indicates character synchronization is complete and will be retained for the message block. In the two-sync-character mode, the receiver searches for the first sync code match on a bit-by-bit basis and then looks for a second successive sync code character prior to establishing character synchronization. If the second sync code character is not received, the bit-by-bit search for the first sync code is resumed.

Sync codes received prior to the completion of synchronization (one or two character) are not transferred to the Receive Data FIFO. Redundant sync codes during the preamble or sync codes which occur as "fill characters" can automatically be stripped from the data, when the Strip Sync control bit is set, to minimize system loading. The character synchronization will be retained until cleared by means of the Clear Sync bit, which also inhibits synchronization search when set.

#### **RECEIVING DATA**

Once synchronization has been achieved, subsequent characters are automatically transferred into the Receive Data FIFO and clocked through the FIFO to the last empty location by E pulses (MPU System  $\phi$ 2). The Receiver Data Available status bit (RDA) indicates when data is available to be read from the last FIFO location (#3) when in the 1-byte transfer mode. The 2-byte transfer mode causes the RDA status bit to indicate data is available when the last two FIFO

register locations are full. Data being available in the Receive Data FIFO causes an interrupt request if the Receiver Interrupt Enable (RIE) bit is set. The MPU will then read the SSDA Status Register which will indicate that data is available for the MPU read from the Receive Data FIFO register. The IRQ and RDA status bits are reset by a read from the FIFO. If more than one character has been received. and is resident in the Receive Data FIFO, subsequent E clocks will cause the FIFO to update and the RDA and IRQ status bits will again be set. The read data operation for the 2-byte transfer mode requires an intervening E clock between reads to allow the FIFO data to shift. Optional parity is automatically checked as data is received, and the parity status condition is maintained with each character until the data is read from the Receive Data FIFO. Parity errors will cause an interrupt request if the Error Interrupt Enable (EIE) has been set. The parity bit is not transferred to the data bus but must be checked in the Status Register. NOTE: In the 2-byte transfer mode, parity should be checked prior to reading the second byte, since a FIFO read clears the error bit.

Other status bits which pertain to the receiver section are Receiver Overrun and Data Carrier Detect (DCD). The Overrun status bit is automatically set when a transfer of a character to the Receive Data FIFO occurs and the first register of the Receive Data FIFO is full. Overrun causes an interrupt if Error Interrupt Enable (EIE) has been set. The transfer of the overrunning character into the FIFO causes the previous character in the FIFO input register location to be lost. The Overrun status bit is cleared by reading the Status Register (when the overrun condition is present), followed by a Receive data FIFO Register read. Overrun cannot occur and be cleared without providing an opportunity to detect its occurrence via the Status Register.

A positive transition on the  $\overline{\text{DCD}}$  input causes an interrupt if the EIE control bit has been set. The interrupt caused by  $\overline{\text{DCD}}$  is cleared by reading the Status Register when the  $\overline{\text{DCD}}$ status bit is high, followed by a Receive data FIFO read. The  $\overline{\text{DCD}}$  status bit will subsequently follow the state of the  $\overline{\text{DCD}}$ input when it goes low.

#### INPUT/OUTPUT FUNCTIONS

#### SSDA INTERFACE SIGNALS FOR MPU

The SSDA interfaces to the MC6800 MPU with an 8-bit bidirectional data bus, a chip-select line, a register-select line, an interrupt-request line, read/write line, an enable line, and a reset line. These signals, in conjunction with the MC6800 VMA output, permit the MPU to have complete control over the SSDA.

SSDA Bi-Directional Data (D0-D7) — The bi-directional data lines (D0-D7) allow for data transfer between the SSDA and the MPU. The data bus output drivers are three-state devices that remain in the high-impedance (off) state except when the MPU performs an SSDA read operation.

SSDA Enable (E) — The Enable signal, E, is a highimpedance TTL-compatible input that enables the bus input/output data buffers, clocks data to and from the SSDA, and moves data through the FIFO Registers.

**Read/Write** (R/W) – The Read/Write line is a highimpedance input that is TTL compatible and is used to control the direction of data flow through the SSDA's input/output data bus interface. When Read/Write is high (MPU read cycle), SSDA output drivers are turned on if the chip is selected and a selected register is read. When it is low, the SSDA output drivers are turned off and the MPU writes into a selected register. The Read/Write signal is also used to select read-only or write-only registers within the SSDA.

Chip Select  $(\overline{CS})$  — This high-impedance TTL-compatible input line is used to address the SSDA. The SSDA is selected when  $\overline{CS}$  is low. VMA should be used in generating the  $\overline{CS}$  input to insure that false selects will not occur. Transfers of data to and from the SSDA are then performed under the control of the Enable signal, Read/Write, and Register Select.

Register Select (RS) — The Register Select line is a highimpedance input that is TTL compatible. A high level is used to select Control Registers C2 and C3, the Sync Code Register, and the Transmit/Receive Data Registers. A low level selects the Control 1 and Status Registers (see Table 1).

**Interrupt Request (IRQ)** – Interrupt Request is a TTL compatible, open-drain (no internal pullup), active low output that is used to interrupt the MPU. The Interrupt Request remains low until cleared by the MPU.

**RESET** Input – The RESET input provides a means of resetting the SSDA from an external source. In the low state, the RESET input causes the following:

- 1. Receiver Reset (Rx Rs) and Transmitter Reset (Tx Rs) bits are set causing both the receiver and transmitter sections to be held in a reset condition.

- 2. Peripheral Control bits PC1 and PC2 are reset to zero, causing the SM/DTR output to be high.

- 3. The Error Interrupt Enable (EIE) bit is reset.

- 4. An internal synchronization mode is selected.

- The Transmitter Data Register Available (TDRA) status bit is cleared and inhibited.

- 6. The Receiver Shift Register is set to 1's.

When RESET returns high (the inactive state), the transmitter and receiver sections will remain in the reset state until the Receiver Reset and Transmitter Reset bits are cleared via the data bus under software control. The control Register bits affected by RESET (Rx Rs, Tx Rs, PC1, PC2, EIE, and E/1 Sync) cannot be changed when RESET is low.

#### CLOCK INPUTS

Separate high-impedance TTL-compatible inputs are provided for clocking of transmitted and received data.

Transmit Clock (Tx CLK) – The Transmit Clock input is used for the clocking of transmitted data. The transmitter shifts data on the negative transition of the clock.

**Receive Clock (Rx CLK)** – The Receive Clock input is used for clocking in received data. The clock and data must be synchronized externally. The receiver samples the data on the positive transition of the clock.

#### SERIAL INPUT/OUTPUT LINES

**Receive Data (Rx Data)** – The Receive Data line is a highimpedance TTL-compatible input through which data is received in a serial format.

Transmit Data (Tx Data) - The Transmit Data output line transfers serial data to a modem or other peripheral

#### PERIPHERAL/MODEM CONTROL

The SSDA includes several functions that permit limited control of a peripheral or modem. The functions included are Clear-to-Send, Sync Match/Data Terminal Ready, Data Carrier Detect, and Transmitter Underflow.

Clear-to-Send ( $\overline{CTS}$ ) — The  $\overline{CTS}$  input provides a realtime inhibit to the transmitter section (the Tx Data FIFO is not disturbed). A positive  $\overline{CTS}$  transition resets the Tx Shift Register and inhibits the TDRA status bit and its associated interrupt in both the one-sync-character and two-synccharacter modes of operation. TDRA is not affected by the  $\overline{CTS}$  input in the external sync mode.

The positive transition of  $\overline{\text{CTS}}$  is stored within the SSDA to insure that its occurrence will be acknowledged by the system. The stored  $\overline{\text{CTS}}$  information and its associated  $\overline{\text{IRO}}$  (if enabled) are cleared by writing a "1" in the Clear  $\overline{\text{CTS}}$  bit in Control Register 3 or in the Transmitter Reset bit. The  $\overline{\text{CTS}}$  status bit subsequently follows the  $\overline{\text{CTS}}$  input when it goes low.

The  $\overline{\text{CTS}}$  input provides character timing for transmitter data when in the external sync mode. Transmission is initiated on the negative transition of the first *full* positive clock pulse of the transmitter clock (Tx CLK) after the release of  $\overline{\text{CTS}}$  (see Figure 6).

Data Carrier Detect ( $\overline{DCD}$ ) — The  $\overline{DCD}$  input provides a real-time inhbit to the receiver section (the Rx FIFO is not disturbed). A positive  $\overline{DCD}$  transition resets and inhibts the receiver section except for the Receive FIFO and the RDRA status bit and its associated  $\overline{IRQ}$ .

The positive transition of DCD is stored within the SSDA to insure that its occurrence will be acknowledged by the system. The stored DCD information and its associated IRQ (if enabled) are cleared by reading the Status Register and then the Receiver FIFO, or by writing a "1" into the Receiver Reset bit. The DCD status bit subsequently follows the DCD input when it goes low. The DCD input provides character synchronization timing for the receiver during the external sync mode of operation. The receiver will be initialized and data will be sampled on the positive transition of the first *full* Receive Clock cycle after release of DCD (see Figure 7).

Sync Match/Data Terminal Ready  $(SM/\overline{DTR})$  – The SM/DTR output provides four functions (see Table 1) depending on the state of the PC1 and PC2 control bits. When the Sync Match mode is selected (PC="1", PC2="0"), the output provides a one-bit-wide pulse when a sync code is detected. This pulse occurs for each sync code match even if the receiver has already attained synchronization. The SM output is inhibited when PC2="1". The DTR mode (PC1="0") provides an output level corresponding to the complement of PC2 ( $\overline{DTR}$ ="0" when PC2="1"). (See Table 1.)

# Mesista

| Register              |    | ntrol<br>outs | Add<br>Con | tress<br>trol | Register Content                      |                                                       |                                          |                                             |                                                       |                                              |                                                                                         |                                                          |

|-----------------------|----|---------------|------------|---------------|---------------------------------------|-------------------------------------------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------|

| nogistat              | RS | R/W           | AC2        | AC1           | Bit 7                                 | Bit 6                                                 | Bit 5                                    | Bit 4                                       | Bit 3                                                 | Bit 2                                        | Bit 1                                                                                   | Bit 0                                                    |

| Status (S)            | 0  | 1             | x          | x             | Interrupt<br>Request<br>(IRQ)         | Receiver<br>Parity<br>Error<br>(PE)                   | Receiver<br>Overrun<br>(Rx Ovin)         | Transmitter<br>Underflow<br>(TUF)           | Clear-to-<br>Send<br>(CTS)                            | Data Carrier<br>Detect<br>(DCD)              | Transmitter<br>Data<br>Register<br>Available<br>(TDRA)                                  | Receiver<br>Data<br>Available<br>(RDA)                   |

| Control 1<br>(C1)     | 0  | 0             | x          | ×             | Address<br>Control 2<br>(AC2)         | Address<br>Control 1<br>(AC1)                         | Receiver<br>Interrupt<br>Enable<br>(RIE) | Transmitter<br>Interrupt<br>Enable<br>(TIE) | Clear<br>Sync                                         | Strip Sync<br>Characters<br>(Strip Sync)     | Transmitter<br>Reset<br>(Tx Rs)                                                         | Receiver<br>Reset<br>(Rx Rs)                             |

| Receive<br>Data FIFO  | 1  | 1             | Х          | Х             | D7                                    | D6                                                    | D5                                       | D4                                          | D3                                                    | D2                                           | D1                                                                                      | D0                                                       |

| Control 2<br>(C2)     | 1  | 0             | 0          | 0             | Error<br>Interrupt<br>Enable<br>(EIE) | Transmit<br>Sync Code<br>on<br>Underflow<br>(Tx Sync) | Word<br>Length<br>Select 3<br>(WS3)      | Word<br>Length<br>Select 2<br>(WS2)         | Word<br>Length<br>Select 1<br>(WS1)                   | 1-Byte/2-Byte<br>Transfer<br>(1-Byte/2-Byte) | Peripheral<br>Control 2<br>(PC2)                                                        | Periphera<br>Control<br>(PC1)                            |

| Control 3<br>(C3)     | 1  | 0             | 0          | 1             | Not Used                              | Not Used                                              | Not Used                                 | Not Used                                    | Clear<br>Transmitter<br>Underflow<br>Status<br>(CTUF) | Clear CTS<br>Status<br>(Clear CTS)           | One-Sync-<br>Character/<br>Two-Sync<br>Character<br>Mode Control<br>(1 Sync/<br>2 Sync) | External<br>Internal<br>Sync Moo<br>Control<br>(E/I Sync |

| Sync Code             | 1  | 0             | 1          | 0             | D7                                    | D6                                                    | D5                                       | D4                                          | D3                                                    | D2                                           | D1                                                                                      | D0                                                       |

| Transmit<br>Data FIFO | 1  | 0             | 1          | 1             | D7                                    | D6                                                    | D5                                       | D4                                          | D3                                                    | D2                                           | D1                                                                                      | D0                                                       |

#### X = Don't care

#### STATUS REGISTER

| IRQ   | Bit 7     | cleared  | RQ flag is cleared when the source of the IRQ is<br>d. The source is determined by the enables in the<br>pl Registers: TIE, RIE, EIE. |

|-------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

|       | Bits 6-0  | reset a  | te the SSDA status at a point in time, and can be<br>is follows:                                                                      |

|       | PE        | Bit 6    | Read Rx Data FIFO, or a "1" into Rx Rs (C1 Bit 0).                                                                                    |

|       | Rx Ovrn   | Bit 5    | Read Status and then Rx Data FIFO, or a "1" into<br>Rx Rs (C1 Bit 0).                                                                 |

|       | TUF       | Bit 4    | A "1" into CTUF (C3 Bit 3) or into Tx Rs (C1 Bit 1).                                                                                  |

|       | CTS       | Bit 3    | A "1" into Clear CTS (C3 Bit 2) or a "1" into Tx Rs<br>(C1 Bit1)                                                                      |

|       | DCD       | Bit 2    | Read Status and then Rx Data FIFO or a "1" into<br>Rx Rs (C1 Bit 0)                                                                   |

|       | TDRA      | Bit 1    | Write into Tx Data FIFO.                                                                                                              |

|       | RDA       | Bit 0    | Read Rx Data FIFO.                                                                                                                    |

| CONT  | TROL REG  | GISTER   | 1                                                                                                                                     |

| AC2,  | AC1 B     | its 7, 6 | Used to access other registers, as shown above.                                                                                       |

| RIE   | 4         |          | When "1", enables interrupt on RDA (S Bit 0).                                                                                         |

| TIE   | N and     | Bit 4    | When "1", enables interrupt on TDRA (S Bit 1).                                                                                        |

| Clear | Sync      |          | When "1", clears receiver character synchronization.                                                                                  |

| Strip | Sync      | Bit 2    | When "1", strips all sync codes from the received data stream.                                                                        |

| Tx R  | 5         | Bit 1    |                                                                                                                                       |

| Rx R  | S         | Bit O    | When "1", resets and inhibits the receiver section.                                                                                   |

| CON.  | TROL REG  | GISTER   | 3 3                                                                                                                                   |

| CTU   | =         | Bit 3    | When "1", clears TUF (S Bit 4), and IRQ if enabled.                                                                                   |

| Clear | CTS       | Bit 2    |                                                                                                                                       |

| 1 Syr | nc/2 Sync | Bit 1    | When "1", selects the one-sync-character mode; when                                                                                   |

|       |           |          | "0", selects the two-sync-character mode.                                                                                             |

| E/I S | упс       | Bit O    |                                                                                                                                       |

|       |           |          | selects the internal sync mode.                                                                                                       |

|       |           |          |                                                                                                                                       |

### CONTROL REGISTER 2

| EIE       | Bit 7    | When "1", enables the PE, Rx Ovrn,<br>TUF, CTS, and DCD interrupt flags                                                                                                                   |

|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |          | (S Bits 6 through 2).                                                                                                                                                                     |

| Tx Sync   | Bit 6    | When "1", allows sync code contents<br>to be transferred on underflow, and<br>enables the TUF Status bit and out-<br>put. When "0", an all mark character<br>is transmitted on underflow. |

| WS3, 2, 1 | Bits 5-3 | Word Length Select                                                                                                                                                                        |

|           |          |                                                                                                                                                                                           |

| Bit 5<br>WS3 | Bit 4<br>WS2                           | Bit 3<br>WS1                    | Word Length                                                                                 |

|--------------|----------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------|

| 0            | 0                                      | 0                               | 6 Bits + Even Parity                                                                        |

| 0            | 0                                      | 1                               | 6 Bits + Odd Parity                                                                         |

| 0            | 1                                      | 0                               | 7 Bits                                                                                      |

| 0            | 1                                      | 1                               | 8 Bits                                                                                      |

| 1            | 0                                      | 0                               | 7 Bits + Even Parity                                                                        |

| 1            | 0                                      | 1                               | 7 Bits + Odd Parity                                                                         |

| 1            | 1                                      | 0                               | 8 Bits + Even Parity                                                                        |

| 1            | 1                                      | 1                               | 8 Bits + Odd Parity                                                                         |

| Byte/2       | Byte                                   | Bit 2                           | When "1", enables th<br>RDA bits to indicate<br>transfer can occur; w                       |

|              | WS3<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | WS3 WS2   0 0   0 1   0 1   1 0 | WS3 WS2 WS1   0 0 0   0 0 1   0 1 0   0 1 1   1 0 0   1 0 1   1 0 1   1 1 0   1 1 1   1 1 1 |

1-Byte/2-Byte Bit 2 When "1", enables the TDRA and RDA bits to indicate when a 1-byte transfer can occur; when "0", the TDRA and RDA bits indicate when a 2-byte transfer can occur. PC2, PC1 Bits 1-0 SM/DTR Output Control

| Bit 1<br>PC2 | Bit 0<br>PC1 | SM/DTR Output at Pin 5 |

|--------------|--------------|------------------------|

| 0<br>0       | 0<br>1       | Pulse1 Bit Wide, on SM |

| 1<br>1       | 0<br>1       | 0<br>SM Inhibited, 0   |

NOTE: When the SSDA is used in applications requiring the MSB of data to be received and transmitted first, the data bus inputs to the SSDA may be reversed (D0 to D7, etc.). Caution must be used when this is done since the bit positions in this table will be reversed, and the parity should not be selected.

Transmitter Underflow (TUF) — The Underflow output indicates the occurrence of a transfer of a "fill character" to the Transmitter Shift Register when the last location (#3) in the Transmit Data FIFO is emtpy. The Underflow output pulse is approximately one Tx CLK high period wide and occurs during the last half of the last bit of the character preceding the "Underflow" (see Figure 4). The Underflow output pulse does not occur when the Tx Sync bit is in the reset state.

#### SSDA REGISTERS

Seven registers in the SSDA can be accessed by means of the data bus. The registers are defined as read-only or writeonly according to the direction of information flow. The Register Select input (RS) selects two registers in each state, one being read-only and the other write-only. The Read/Write input (R/W) defines which of the two selected registers will actually be accessed. Four registers (two read-only and two write-only) can be accessed via the bus at any particular time. These registers and the required addressing are defined in Table 1.

#### CONTROL REGISTER 1 (C1)

Control Register 1 is an 8-bit write-only register that can be directly addressed from the data bus. Control Register 1 is accessed when RS = "0" and R/W = "0".

Receiver Reset (Rx Rs), C1 Bit 0 – The Receiver Reset control bit provides both a reset and inhibit function to the receiver section. When Rx Rs is set, it clears the receiver control logic, sync logic, error logic, Rx Data FIFO Control, Parity Error status bit, and DCD interrupt. The Receiver Shift Register is set to ones. The Rx Rs bit must be cleared after the occurrence of a low level on RESET in order to enable the receiver section of the SSDA.

Transmitter Reset (Tx Rs), C1 Bit 1 — The Transmitter Reset control bit provides both reset and inhibit to the transmitter section. When Tx Rs is set, it clears the transmitter control section, Transmitter Shift Register, Tx Data FIFO Control (the Tx Data FIFO can be reloaded after one E clock pulse), the Transmitter Underflow status bit, and the CTS interrupt, and inhibits the TDRA status bit (in the one-synccharacter and two-sync-character modes). The Tx Rs bit must be cleared after the occurrence of a low level on RESET in order to enable the transmitter section of the SSDA. If the Tx FIFO is not preloaded, it must be loaded immediately after the Tx Rs release to prevent a transmitter underflow condition.

Strip Synchronization Characters (Strip Sync), C1 Bit 2 – If the Strip Sync bit is set, the SSDA will automatically strip all received characters which match the contents of the Sync Code Register. The characters used for synchronization (one or two characters of sync) are always stripped from the received data stream.

Clear Synchronization (Clear Sync), C1 Bit 3 – The Clear Sync control bit provides the capability of dropping receiver character synchronization and inhibiting resynchronization. The Clear Sync bit is set to clear and inhibit receiver synchronization in *all* modes and is reset to zero to enable resynchronization.

Transmitter Interrupt Enable (TIE), C1 Bit 4 – TIE enables both the Interrupt Request output ( $\overline{IRQ}$ ) and Interrupt Request status bit to indicate a transmitter service request. When TIE is set and the TDRA status bit is high, the  $\overline{IRQ}$  output will go low (the active state) and the  $\overline{IRQ}$  status bit will go high.

Receiver Interrupt Enable (RIE), C1 Bit 5 – RIE enables both the Interrupt Request output (IRO) and the Interrupt Request status bit to indicate a receiver service request. When RIE is set and the RDA status bit is high, the IRO output will go low (the active state) and the IRO status bit will go high.

Address Control 1 (AC1) and Address Control 2 (AC2), C1 Bits 6 and 7 – AC1 and AC2 select one of the write-only registers – Control 2, Control 3, Sync Code, or Tx Data FIFO – as shown in Table 1, when RS = "1" and R/W = "0".

#### CONTROL REGISTER 2 (C2)

Control Register 2 is an 8-bit write-only register which can be programmed from the data bus when the Address Control bits in Control Register 1 (AC1 and AC2) are reset, RS = "1" and R/W = "0".

Peripheral Control (PC1) and Peripheral Control 2 (PC2), C2 Bits 0 and 1 – Two control bits, PC1 and PC2, determine the operating characteristics of the Sync Match/ $\overline{\text{DTR}}$  output. PC1, when high, selects the Sync Match mode. PC2 provides the inhibit/enable control for the SM/ $\overline{\text{DTR}}$  output in the Sync Match mode. A one-bit-wide pulse is generated at the output when PC2 is "0", and a match occurs between the contents of the Sync Code Register and the incoming data even if sync is inhibited (Clear Sync bit="1"). The Sync Match pulse is referenced to the negative edge of Rx -CLK pulse causing the match (see Figure 3).

The Data Terminal Ready  $(\overline{\text{DTR}})$  mode is selected when PC1 is low. When PC2 = "1" the SM/ $\overline{\text{DTR}}$  output = "0" and vice versa. The operation of PC2 and PC1 is summarized in Table 1.

1-Byte/2-Byte Transfer (1-Byte/2-Byte), C2, Bit 2 — When 1-Byte/2-Byte is set, the TDRA and RDA status bits will indicate the availabitily of their respective data FIFO registers for a single-byte data transfer. Alternately, if 1-Byte/2-Byte is reset, the TDRA and RDA status bits indicate when two bytes of data can be moved without a second status read. An intervening Enable pulse must occur between data transfers.

Word Length Selects (WS1, WS2, WS3), C2 Bits 3, 4, 5 - Word Length Select bits WS1, WS2, and WS3 select word lengths of 7, 8, or 9 bits including parity as shown in Table 1.

Transmit Sync Code on Underflow (Tx Sync), C2 Bit 6 – When Tx Sync is set, the transmitter will automatically send a sync character when data is not available for transmission. If Tx Sync is reset, the transmitter will transmit a Mark character (including the parity bit position) on underflow. When the underflow is detected, a pulse approximately one Tx CLK high period wide will occur on the underflow output

**MOTOROLA** Semiconductor Products Inc.

if the Tx Sync bit is set. Internal parity generation is inhibited during underflow except for sync code fill character transmission in 8-bit plus parity word lengths.

Error Interrupt Enable (EIE), C2 Bit 7 - When EIE is set, the IRQ status bit will go high and the IRQ output will go low if:

- A receiver overrun occurs. The interrupt is cleared by reading the Status Register and reading the Rx Data FIFO.

- DCD input has gone to a "1". The interrupt is cleared by reading the Status Register and reading the Rx Data FIFO.

- 3. A parity error exists for the character in the last location (#3) of the Rx Data FIFO. The interrupt is cleared by reading the Rx Data FIFO.

- The CTS input has gone to a "1". The interrupt is cleared by writing a "1" in the Clear CTS bit, C3 bit 2, or by a Tx Reset.

- The transmitter has underflowed (in the Tx Sync on Underflow mode). The interrupt is cleared by writing a "1" into the Clear Underflow, C3 bit 3, or Tx Reset.

When EIE is a "0", the  $\overline{IRQ}$  status bit and the  $\overline{IRQ}$  output are disabled for the above error conditions. A low level on the  $\overline{RESET}$  input resets EIE to "0".

#### CONTROL REGISTER 3 (C3)

18 2: 24

Control Register 3 is a 4-bit write-only register which can be programmed from the data bus whe RS = "1" and R/W = "0" and Address Control bit AC1 = "1" and AC2 = "0".

External/Internal Sync Mode Conrol (E/I Sync), C3, Bit 0 — When the E/I Sync Mode bit is high, the SSDA is in the external sync mode and the receiver synchronization logic is disabled. Synchronization can be achieved by means of the DCD input or by starting Rx CLK at the midpoint of data bit 0 of a cahracter with DCD low. Both the transmitter and receiver sections operate as parallel — serial converters in the External Sync mode. The Clear Sync bit in Control Register 1 acts as a receiver sync inhibit when high to provide a bus controllable inhibit. The Sync Code Register can serve as a transmitter fill character register and a receiver match register in this mode. A "low" on the RESET input resets the E/I Sync Mode bit placing the SSDA in the internal sync mode.

One-Sync-Character/Two-Sync-Character Mode Control (1-Sync/2-Sync), C3 Bit 1 — When the 1-Sync/2-Sync bit is set, the SSDA will synchronize on a single match between the received data and the contents of the Sync Code Register. When the 1-Sync/2-Sync bit is reset, two *successive* sync characters must be received prior to receiver synhnchronization. If the second sync character is not detected, the bit-by-bit search resumes from the first bit in the second character. See the description of the Sync Code Register for more details.

Clear  $\overline{\text{CTS}}$  Status (Clear  $\overline{\text{CTS}}$ ), C3 Bit 2 — When a "1" is written into the Clear  $\overline{\text{CTS}}$  bit, the stored status and interrupt are cleared. Subsequently, the  $\overline{\text{CTS}}$  status bit reflects the

state of the  $\overline{\text{CTS}}$  input. The Clear  $\overline{\text{CTS}}$  control bit does not affect the  $\overline{\text{CTS}}$  input nor its inhibit of the transmitter section. The Clear  $\overline{\text{CTS}}$  command bit is self-clearing, and writing a "0" into this bit is a nonfunctional operation.

Clear Transmit Underflow Status (CTUF), C3 Bit 3 – When a "1" is written into the CTUF status bit, the CTUF bit and its associated interrupt are reset. The CTUF command bit is self-clearing and writing a "0" into this bit is a nonfunctional operation.

#### SYNC CODE REGISTER

The Sync Code Register is an 8-bit register for storing the programmable sync code required for received data character synchronization in the one-sync-character and two-synccharacter modes. The Sync Code Register also provides for stripping the sync/fill characters from the received data (a programmable option) as well as automatic insertion of fill characters in the transmitted data stream. The Sync Code Register is not utilized for receiver character synchronization in the external sync mode; however, it provides storage of receiver match and transmit fill characters.

The Sync Code Register can be loaded when AC2 and AC1 are a "1" and "0", respectively, and R/W = "0" and RS = "1".

The Sync Code Register may be changed after the detection of a match with the received data (the first sync code having been detected) to synchronize with a double-word sync pattern. (This sync code change must occur prior to the completion of the second character.) The sync match (SM) output can be used to interrupt the MPU system to indicate that the first eight bits have matched. The service routine would then change the sync match register to the second half of the pattern. Alternately, the one-sync-character mode can be used for sync codes for 16 or more bits by using software to check the second and subsequent bytes after reading them from the FIFO.

The detection of the sync code can be programmed to appear on the Sync Match/DTR output by writing a "1" in PC1 (C2 bit 0) and a "0" in PC2 (C2 bit 1). The Sync Match output will go high for one bit time beginning at the character interface between the sync code and the next character (see Figure 3).

#### PARITY FOR SYNC CHARACTER

#### Transmitter

Transmitter does not generate parity for the sync character except 9-bit mode.

9-bit (8-bit + parity)...8-bit sync character + parity 8-bit (7-bit + parity)...8-bit sync character (no parity)

7-bit (6-bit + parity)...7-bit sync character (no parity)

#### Receiver

At Synchronization

Receiver automatically strips the sync character(s) (two sync characters if '2 sync' mode is selected) which is used to establish synchronization. Parity is not checked for these sync characters.

**MOTOROLA** Semiconductor Products Inc.

#### After Synchronization Is Established

When 'strip sync' bit is selected, the sync characters (fill characters) are stripped and parity is not checked for the stripped sync (fill) characters. When "strip sync" bit is not selected (low), the sync character is assumed to be normal data and it is transferred into FIFO after parity checking. (When non-parity format is selected, parity is not checked.)

| Strip Sync<br>(C1, Bit 2) | WS0-WS2<br>(Data Format)<br>(C2, Bits 3-5) |                                                          |

|---------------------------|--------------------------------------------|----------------------------------------------------------|

| 1                         | х                                          | No transfer of sync code<br>No parity Check of sync code |

| 0                         | With Parity                                | *Transfer data and sync codes<br>Parity check            |

| 0                         | Without Parity                             | *Transfer data and sync codes<br>No parity check         |

\*Subsequent to synchronization.

It is necessary to consider parity in the selected sync character in the following cases. Data Format is (6+parity), (7+parity), strip sync is not selected (low), and when sync code is used as a fill character after synchronization.

The transmitter sends a sync character without parity, but the receiver checks the parity as if it is normal data. Therefore, the sync character should be chosen to match the parity check selected for the receiver in this special case. See the following section for unused bit assignment in shortword length.

# RECEIVE DATA FIRST-IN FIRST-OUT REGISTER (Rx Data

The Receive Data FIFO Register consists of three 8-bit registers which are used for buffer storage of received data. Each 8-bit register has an internal status bit which monitors its full or empty condition. Data is always transferred from a full register to an adjacent empty register. The transfer from register to register occurs on E pulses. The RDA status bit will be high when data is available in the last location of the Rx Data FIFO.

In an Overrun condition, the overrunning character will be transferred into the full first stage of the FIFO register and will cause the loss of that data character. Successive overruns continue to overwrite the first register of the FIFO. This destruction of data is indicated by means of the Overrun status bit. The Overrun bit will be set when the overrun occurs and remains set until the Status Register is read, followed by a read of the Rx Data FIFO.

Unused data bits for short word lengths (including the parity bit) will appear as "0's" on the data bus when the Rx Data FIFO is read.

# TRANSMIT DATA FIRST-IN FIRST-OUT REGISTER (Tx Data FIFO)

The Transmit Data FIFO Register consists of thee 8-bit registers which are used for buffer storage of data to be transmitted. Each 8-bit register has an internal status bit which monitors its full or empty condition. Data is always transferred from a full register to an adjacent empty register. The transfer is clocked by E pulses.

The TDRA status bit will be high if the Tx Data FIFO is available for data.

Unused data bits for short word lengths will be handled as "don't cares." The parity bit is not transferred over the data bus since the SSDA generates parity at transmission.

When an Underflow occurs, the Underflow character will be either the contents of the Sync Code Register or an all "1's" character. The underflow will be stored in the Status Register until cleared and will appear on the Underflow output as a pulse approximatley one Tx CLK high period wide.

#### STATUS REGISTER (S)

The Status Register is an 8-bit read-only register which provides the real-time status of the SSDA and the associated serial data channel. Reading the Status Register is a nondestructive process. The method of clearing status bits depends upon the function each bit represents and is discussed for each bit in the register.

**Receiver Data Available (RDA), S Bit 0** – The Receiver Data Available status bit indicates when receiver data can be read from the Rx Data FIFO. The receiver data being present in the last register (#3) of the FIFO causes RDA to be high for the 1-byte transfer mode. The RDA bit being high indicates that the last two registers (#2 and #3) are full when in the 2-byte transfer mode. The second character can be read without a second status read (to determine that the character is available). An E pulse must occur between reads of the Rx Data FIFO to allow the FIFO to shift. Status must be read on a word-by-word basis if receiver data error checking is important. The RDA status bit is reset automatically when data is not available.

Transmitter Data Register Available (TDRA), S Bit 1 -The TDRA status bit indicates that data can be loaded into the Tx Data FIFO Register. The first register (#1) of the Tx Data IFFO being empty will be indicated by a high level in the TDRA status bit in the 1-byte transfer mode. The first two registers (#1 and #2) must be empty for TDRA to be high when in the 2-byte transfer mode. The Tx Data FIFO can be loaded with two bytes without an intervening status read; however, one E pulse must occur between loads. TDRA is inhibited by the Tx Reset or RESET. When Tx Reset is set, the Tx Data FIFO is cleared and then released on the next E clock pulse. The Tx Data FIFO can then be loaded with up to three characters of data, even though TDRA is inhibited. This feature allows preloading data prior to the release of Tx Reset. A high level on the CTS input inhibits the TDRA status bit in either sync mode of operation (one-synccharacter or two-sync-character). CTS does not affect TDRA in the external sync mode. This enables the SSDA to operate under the control of the CTS input with TDRA indicating the status of the Tx Data FIFO. The CTS input does not clear the Tx Data FIFO in any operating mode.

Data Carrier Detect ( $\overline{DCD}$ ), S Bit 2 – A positive transition on the DCD input is stored in the SSDA until cleared by reading both Status and Rx Data FIFO. A "1" written into Rx Rs also clears the stored  $\overline{DCD}$  status. The  $\overline{DCD}$  status bit, when set, indicates that the  $\overline{DCD}$  input has gone high. The reading of Status followed by reading of the Receive Data FIFO allows Bit 2 of subsequent Status reads to indicate the state of the  $\overline{DCD}$  input until the next positive transition.

# MCCC

**Clear-to-Send** ( $\overline{\text{CTS}}$ ), **S** Bit 3 – A positive transition on the  $\overline{\text{CTS}}$  input is stored in the SSDA until cleared by writing a "1" into the Clear  $\overline{\text{CTS}}$  control bit or the Tx Rs bit. The  $\overline{\text{CTS}}$  status bit, when set, indicates that the  $\overline{\text{CTS}}$  input has gone high. The Clear  $\overline{\text{CTS}}$  command (a "1" into C3 Bit 2) allows Bit 3 of subsequent Status reads to indicate the state of the  $\overline{\text{CTS}}$  input until the next positive transition.

**Transmitter Underflow (TUF), S Bit 4** — When data is not available for the transmitter, an underflow occurs and is so indicated in the Status Register (in the Tx Sync on underflow mode). The underflow status bit is cleared by writing a "1" into the Clear Underflow (CTUF) control bit or the Tx Rs bit. TUF indicates that a sync character will be transmitted as the next character. A TUF is indicated on the output *only* when the contents of the Sync Code Register is to be transferred (transmit sync code on underflow = "1").

Receiver Overrun (Rx Ovrn), S Bit 5 – Overrun indicates data has been received when the Rx Data FIFO is full,

resulting in data loss. The Rx Ovrn status bit is set when overrun occurs. The Rx Ovrn status bit is cleared by reading Status followed by reading the Rx Data FIFO or by setting the Rx Rs control bit.

(

ſ

Receiver Parity Error (PE), S Bit 6 – The parity error status bit indicates that parity for the character in the last register of the Rx Data FIFO did not agree with selected parity. The parity error is cleared when the character to which it pertains is read from the Rx Data FIFO or when Rx Rs occurs. The DCD input does not clear the Parity Error or Rx Data FIFO status bits.

Interrupt Request ( $\overline{IRQ}$ ), S Bit 7 – The Interrupt Request status bit indicates when the  $\overline{IRQ}$  output is in the active state ( $\overline{IRQ}$  output = "0"). The  $\overline{IRQ}$  status bit is subject to the same interrupt enables (RIE, TIE, and EIE) as the  $\overline{IRQ}$  output. The  $\overline{IRQ}$  status bit simplifies status inquiries for polling systems by providing single bit indication of service requests.

Motorola reserves the right to make changes to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

\_\_\_\_\_(**€**≎::⊃2

and the second

-172 -172 -172

1.000

6474 6

٦.

17.2

**NOTOROLA** Semiconductor Products Inc.