### INTEGRATED CIRCUITS

### SHEET

### **TDA3755** PAL/NTSC/SECAM synchronization processor for video recorders

**Product specification** File under Integrated Circuits, IC02

### PAL/NTSC/SECAM synchronization processor for video recorders

**TDA3755**

#### **GENERAL DESCRIPTION**

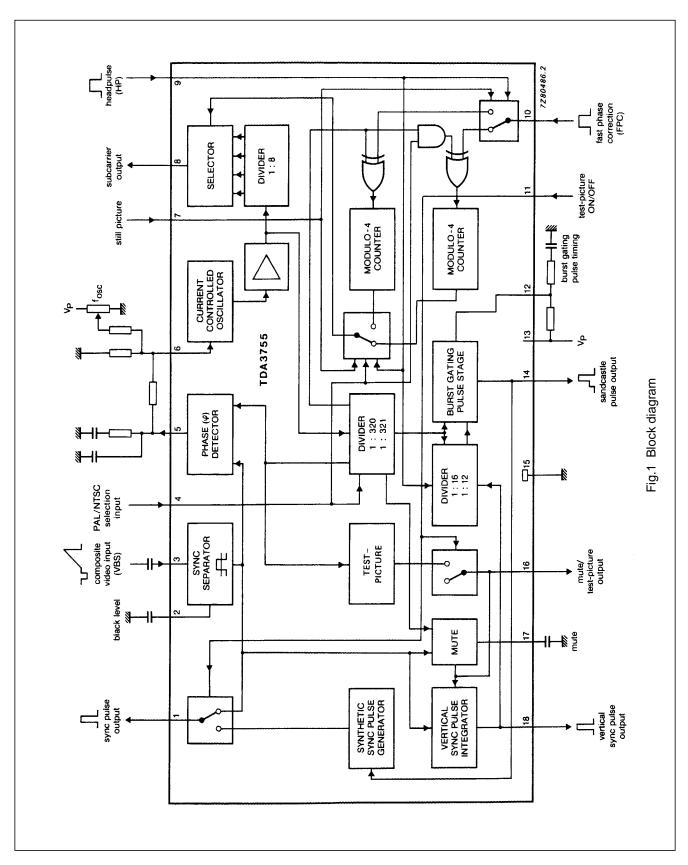

The TDA3755 is a monolithic integrated circuit for PAL/NTSC SECAM synchronization processing in VHS video recorders.

#### **Features**

- · Adaptive sync separator

- · Internal vertical sync pulse integrator

- · Composite sync and vertical pulse output

- Current controlled oscillator (CCO) with 320/321 times horizontal frequency

- · Horizontal phase detector with current output

- · Video identification and mute circuit

- Burst gating pulse output (externally adjustable phase relationship)

- Test-picture output

- Subcarrier frequency output switched in phase in accordance with VHS standard

- Fast phase correction of subcarrier frequency

- Selection input to force PAL or NTSC function

- Still picture input

### **QUICK REFERENCE DATA**

| Supply voltage (pin 13)   | $V_P = V_{13-15}$       | typ. | 10    | V   |

|---------------------------|-------------------------|------|-------|-----|

| Supply current (pin 13)   | $I_{P} = I_{13}$        | typ. | 24    | mA  |

| Sync separator            |                         |      |       |     |

| Sync pulse input voltage  |                         |      |       |     |

| (peak-to-peak value)      | $V_{3-15(p-p)}$         | typ. | 300   | mV  |

| Sync pulse output voltage |                         |      |       |     |

| (peak-to-peak value)      | $V_{1-15(p-p)}$         | min. | 7,3   | V   |

| Vertical sync pulse       |                         |      |       |     |

| Output voltage            |                         |      |       |     |

| (peak-to-peak value)      | V <sub>18-15(p-p)</sub> | min. | 2,7   | V   |

| Phase detector            |                         |      |       |     |

| Catching range            | $\Delta f$              | min. | ± 3,0 | %   |

| Oscillator                |                         |      |       |     |

| Oscillator frequency      |                         |      |       |     |

| PAL                       | f <sub>osc</sub>        | typ. | 5,02  | MHz |

| NTSC                      | f <sub>osc</sub>        | typ. | 5,04  | MHz |

| Output frequency          |                         |      |       |     |

| PAL                       | $f_{o}$                 | typ. | 627   | kHz |

| NTSC                      | $f_{o}$                 | typ. | 629   | kHz |

| Output sinewave           |                         |      |       |     |

| (peak-to-peak value)      | $V_{8-15(p-p)}$         | typ. | 3     | V   |

### PACKAGE OUTLINE

18-lead DIL; plastic (SOT102); SOT102-1; 1996 December 11.

June 1986

## PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

#### PAL/NTSC/SECAM synchronization TDA3755 processor for video recorders **RATINGS** Limiting values in accordance with the Absolute Maximum System (IEC 134) $V_P = V_{13-15}$ Supply voltage (pin 13) max. 13,2 ٧ Voltage range at pins 2, 3, 4, 7, 9, 10, 11, 17 to pin 15 (ground) $V_{n-15}$ 0 to $V_P$ ٧ Voltage range at pin 12 $V_{12-15}$ min. 0 ٧ Voltage range at pin 6 $V_{6-15}$ max. 8 ٧ **Currents** at pins 1, 5, 8, 14, 16, 18 max. 5 $\pm I_n$ mA at pin 6 $-I_{6}$ max. 1 mΑ at pin 12 mΑ $I_{12}$ max. 2 Total power dissipation W $\mathsf{P}_{\mathsf{tot}}$ max. 1

$T_{stg}$

$T_{amb}$

-25 to + 150

0 to + 70

°C

٥С

June 1986 4

Storage temperature range

Operating ambient temperature range

## PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

### **CHARACTERISTICS**

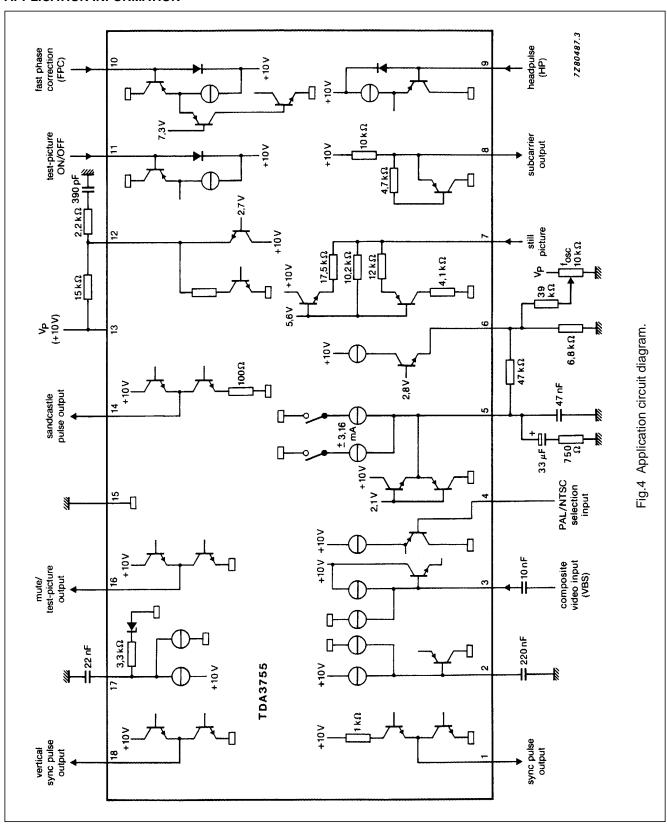

$V_P$  = 10 V;  $T_{amb}$  = 25 °C; measured in Fig.4; unless otherwise specified

| PARAMETER                                                  | SYMBOL                 | MIN. | TYP. | MAX. | UNIT |

|------------------------------------------------------------|------------------------|------|------|------|------|

| Supply (pin 13)                                            |                        |      |      |      |      |

| Supply voltage range                                       | $V_{P} = V_{13-15}$    | 9,6  | _    | 13,2 | V    |

| Supply current                                             | $I_{P} = I_{13}$       | _    | 24   | _    | mA   |

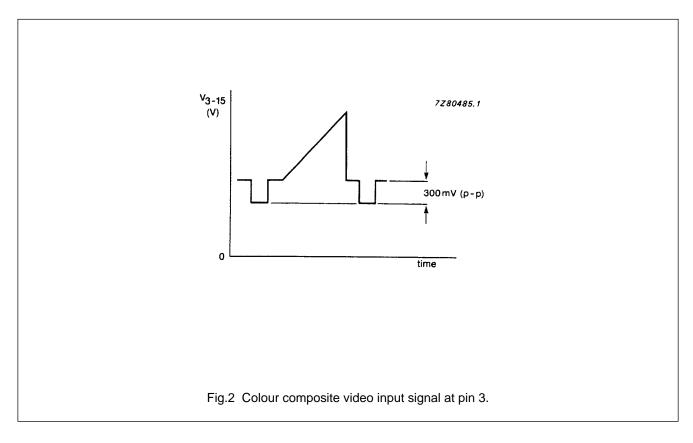

| Sync separator (pin 3)                                     |                        |      |      |      |      |

| Colour composite video                                     |                        |      |      |      |      |

| input voltage (note 2)<br>(peak-to-peak value)             | V <sub>3-15(p-p)</sub> | _    | 1    | _    | V    |

| Sync pulse amplitude                                       |                        |      |      |      |      |

| (peak-to-peak value)                                       | V <sub>3-15(p-p)</sub> | 75   | _    | 600  | mV   |

| Slicing level, relative to                                 |                        |      |      |      |      |

| sync pulse amplitude (note 3)                              |                        | _    | 50   | _    | %    |

| Internal resistance of video source                        | $R_{G}$                | _    | _    | 1    | kΩ   |

| Sync output voltage HIGH                                   |                        |      |      |      |      |

| at $-I_1 = 1 \text{ mA}$                                   | V <sub>1-15</sub>      | 7,8  | _    | _    | V    |

| Sync output voltage LOW                                    |                        |      |      |      |      |

| at I <sub>1</sub> = 1 mA                                   | V <sub>1-15</sub>      | _    | _    | 0,5  | V    |

| Delay between signal                                       |                        |      |      |      |      |

| at input pin 3 and sync pulse at output pin 1              | t <sub>d</sub>         | _    | 0,2  | _    | μs   |

| Vertical sync pulse (pin 18; note 4)                       |                        |      |      |      |      |

| Output voltage HIGH                                        |                        |      |      |      |      |

| at –I <sub>18</sub> = 1 mA                                 | V <sub>18-15</sub>     | 2,7  | _    | 5,0  | V    |

| Output voltage LOW                                         |                        |      |      |      |      |

| at I <sub>18</sub> = 1,6 mA                                | V <sub>18-15</sub>     | _    | _    | 0,5  | V    |

| Duration of HIGH state                                     |                        |      |      |      |      |

| of internally generated output pulse                       | t <sub>p</sub>         | _    | 190  | _    | μs   |

| Delay between leading edge of input                        |                        |      |      |      |      |

| signal at pin 3 and leading edge of output pulse at pin 18 | t <sub>d</sub>         | 32   | _    | 64   | μs   |

| Selection input (pin 4)                                    |                        |      |      |      |      |

| Input voltage for NTSC state                               | V <sub>4-15</sub>      | _    | _    | 0,3  | V    |

| Input current                                              |                        |      |      |      |      |

| at $V_{4-15} = 0 \text{ V}$                                | -I <sub>4</sub>        | _    | _    | 20   | μΑ   |

| Input voltage for PAL state                                |                        |      |      |      |      |

| pin 4 open circuit                                         | V <sub>4-15</sub>      | 2    | _    | _    | V    |

## PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

| PARAMETER                              | SYMBOL                 | MIN.  | TYP.              | MAX. | UNIT            |

|----------------------------------------|------------------------|-------|-------------------|------|-----------------|

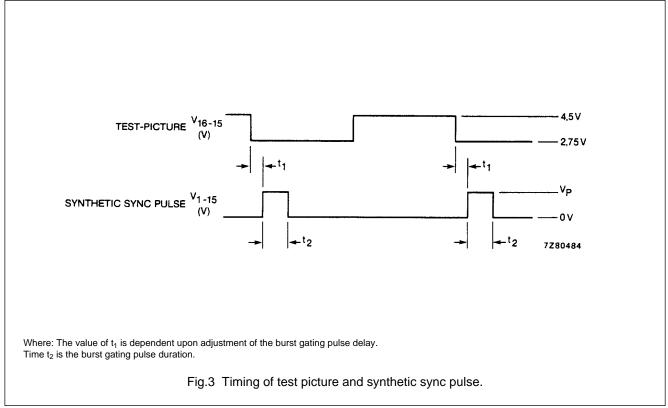

| Test picture/mute/synthetic sync pulse |                        |       |                   |      |                 |

| Minimum voltage at pin 11 for          |                        |       |                   |      |                 |

| test picture mode active (note 5)      | V <sub>11-15</sub>     | 4,8   | _                 | _    | V               |

| Maximum voltage at pin 11 for          |                        |       |                   |      |                 |

| test picture mode inactive             | V <sub>11-15</sub>     | _     | _                 | 3,8  | V               |

| Output voltage at pin 16               |                        |       |                   |      |                 |

| at test picture "black" or at mute     | V <sub>16-15</sub>     | _     | 2,75              | _    | V               |

| at test picture "white"                | V <sub>16-15</sub>     | _     | 4,50              | _    | V               |

| at "in sync condition"                 | V <sub>16-15</sub>     | _     | _                 | 0,5  | V               |

| Input current (pin 11)                 | -I <sub>11</sub>       | _     | _                 | 25   | μΑ              |

| Oscillator/phase detector              |                        |       |                   |      |                 |

| Oscillator frequency (note 6)          |                        |       |                   |      |                 |

| PAL                                    | f <sub>osc</sub>       | _     | 5,02              | _    | MHz             |

| NTSC                                   | f <sub>osc</sub>       | _     | 5,04              | _    | MHz             |

| Oscillator conversion gain             | k <sub>o</sub>         | _     | 16,13             | _    | MHz/mA          |

| D.C. control voltage                   | V <sub>6-15</sub>      | _     | 2,1               | _    | V               |

| Input current for f = 5,016 MHz        | -I <sub>16</sub>       | _     | 310               | _    | μΑ              |

| Holding range (note 7)                 | $\Delta f$             | ± 3,2 | _                 | _    | %               |

| Catching range (note 7)                | $\Delta f$             | ± 3,0 | _                 | _    | %               |

| Control loop gain                      | k <sub>v</sub>         | _     | 380               | _    | s <sup>-1</sup> |

|                                        |                        |       | × 10 <sup>3</sup> |      |                 |

| Output of lower subcarrier (note 8)    |                        |       |                   |      |                 |

| (peak-to-peak value)                   | V <sub>8-15(p-p)</sub> | _     | 3                 | _    | V               |

| Output current                         | I <sub>8</sub>         | _     | _                 | 2    | mA              |

| D.C. output voltage                    | V <sub>8-15</sub>      | _     | 3,1               | _    | V               |

| 2nd harmonic suppression               |                        |       |                   |      |                 |

| without switching                      | $lpha_{2nd}$           | 20    | _                 | _    | dB              |

| Switching position prior to centre     |                        |       |                   |      |                 |

| of sync pulse (pin 3)                  | t <sub>s</sub>         | _     | 2                 | _    | μs              |

| Output peak current of phase detector  |                        |       |                   |      |                 |

| during sync pulse                      | ± I <sub>5</sub>       | -     | 3,78              | _    | mA              |

| Output voltage range (note 9)          | V <sub>5-15</sub>      | 1,4   | _                 | 2,8  | V               |

## PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

| PARAMETER                            | SYMBOL             | MIN. | TYP.               | MAX. | UNIT |

|--------------------------------------|--------------------|------|--------------------|------|------|

| Sandcastle pulse (pin 14; note 10)   |                    |      |                    |      |      |

| Output voltage HIGH (note 11)        |                    |      |                    |      |      |

| at -I <sub>14</sub> =1 mA            | V <sub>14-15</sub> | 7,8  | _                  | _    | V    |

| Output voltage INTERMEDIATE          |                    |      |                    |      |      |

| at -I <sub>14</sub> = 1 mA           | V <sub>14-15</sub> | 2,3  | 3,0                | 3,7  | V    |

| Output voltage LOW                   |                    |      |                    |      |      |

| at I <sub>14</sub> =1 mA             | V <sub>14-15</sub> | _    | _                  | 0,5  | V    |

| Lower part is starting prior to the  |                    |      |                    |      |      |

| centre of sync pulse at pin 3        | t <sub>14-3</sub>  | _    | 2,6                | _    | μs   |

| and ending with the upper part       |                    |      |                    |      |      |

| Fast phase correction/head pulse     |                    |      |                    |      |      |

| Threshold voltage                    |                    |      |                    |      |      |

| for fast phase correction (note 12)  | V <sub>10-15</sub> | _    | 7,2                | _    | V    |

| Input current                        | -I <sub>10</sub>   | _    | _                  | 20   | μΑ   |

| Threshold voltage                    |                    |      |                    |      |      |

| of head pulse input                  | V <sub>9-15</sub>  | _    | 1,4                | _    | V    |

| Input current                        | -l <sub>9</sub>    | _    | _                  | 20   | μΑ   |

| D.C. input voltage                   | V <sub>7-15</sub>  | _    | 5,6                | _    | V    |

| Input resistance                     | R <sub>7-15</sub>  | 3    | _                  | _    | kΩ   |

| Subcarrier phase switching (note 13) |                    |      |                    |      |      |

| Phase switching of subcarrier phase  |                    |      |                    |      |      |

| in accordance with head pulse        | V <sub>7-15</sub>  | _    | 5,6 <sup>(1)</sup> | _    | V    |

| LOW state of still picture input     | V <sub>7-15</sub>  | _    | _                  | 0,5  | V    |

| Continuous phase switching           |                    |      |                    |      |      |

| voltage                              | V <sub>7-15</sub>  | _    | V <sub>P</sub>     | _    | V    |

### PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

#### Notes to the characteristics

- 1. Or not connected.

- 2. The sync separator input signal is shown in Fig.2.

- 3. The black level and the top sync level are detected internally and stored in capacitors at pin 2 and pin 3 respectively.

- 4. The vertical sync pulse output is disabled by mute.

- 5. In test picture mode the synthetic sync pulse is fed to output pin 1 and the vertical pulse consists of an uninterrupted block pulse of 192 μs triggering at every transition of head pulse (HP) at pin 9. The timing of test picture and synthetic sync pulse is shown in Fig.3.

- 6. Oscillator adjustment during test picture mode made only, at  $V_{11-15} > 4.8 \text{ V}$ ,  $V_{7-15} = 0 \text{ V}$  and  $V_{4-15} > 2 \text{ V}$  or open circuit; measurement is  $f_{osc} / 8$  at output pin 8.

- 7. The holding range and catching range are both determined by the resistor connected between pin 5 and pin 6.

- 8. The phase of the lower subcarrier is switched in accordance with the VHS standard. PNP emitter follower, internal resistive load of 10 k $\Omega$  (typ.) to  $V_{P}$ .

- 9. The output voltage at pin 5 is disabled during test picture mode.

- 10. The burst gating pulse is superimposed on an uninterrupted horizontal pulse. It is suppressed 16 times starting with every transition of the head pulse at pin 9. If a vertical pulse is detected during that time the burst gating pulses are additionally suppressed until line 12 and line 324 respectively. In any event the number of suppressed burst gating pulses is even.

- 11. The timing of the upper part of the sandcastle pulse is determined by the components connected to pin 12 (Fig.4) and is independent of supply voltage variations.

- 12. The fast phase correction pulses have to be in the burst gating reference pulse. For any HIGH to LOW transitions of the correction pulse the phase is corrected by –90° if the head pulse input is LOW and by +90° if the head pulse input is HIGH.

- 13. Subcarrier phase switching is detailed in Table 1. Subcarrier is  $40,000 \times f_H$  for NTSC state and  $40,125 \times f_H$  for PAL state.

Table 1 Subcarrier phase switching

| STILL         | P                  | PAL  | NT        | SC       |

|---------------|--------------------|------|-----------|----------|

| PICTURE INPUT | HP = HIGH HP = LOW |      | HP = HIGH | HP = LOW |

| HIGH          | −90°               | -90° | −90°      | −90°     |

| not connected | 0°                 | −90° | +90°      | −90°     |

| LOW           | 0°                 | 0°   | +90°      | +90°     |

### PAL/NTSC/SECAM synchronization processor for video recorders

**TDA3755**

## PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

### **APPLICATION INFORMATION**

# PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

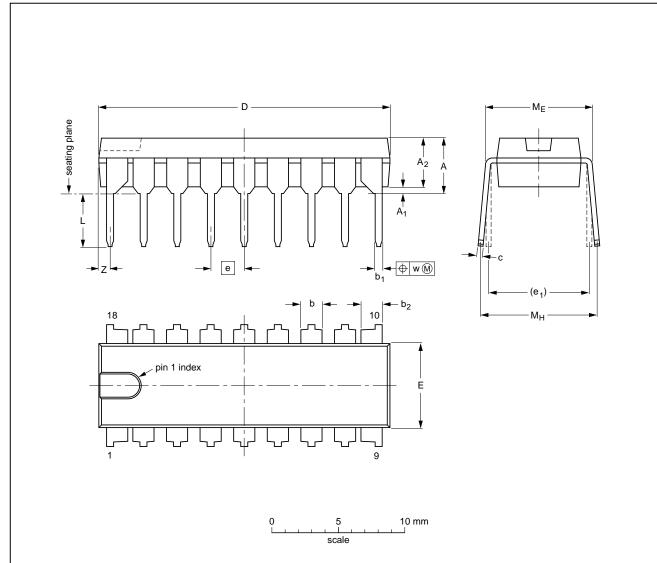

### **PACKAGE OUTLINE**

DIP18: plastic dual in-line package; 18 leads (300 mil)

SOT102-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | b <sub>2</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME           | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|---------------------|------------------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|--------------|-------|--------------------------|

| mm     | 4.7       | 0.51                | 3.7                    | 1.40<br>1.14   | 0.53<br>0.38   | 1.40<br>1.14   | 0.32<br>0.23   | 21.8<br>21.4     | 6.48<br>6.20     | 2.54 | 7.62           | 3.9<br>3.4   | 8.25<br>7.80 | 9.5<br>8.3   | 0.254 | 0.85                     |

| inches | 0.19      | 0.020               | 0.15                   | 0.055<br>0.044 | 0.021<br>0.015 | 0.055<br>0.044 | 0.013<br>0.009 | 0.86<br>0.84     | 0.26<br>0.24     | 0.10 | 0.30           | 0.15<br>0.13 | 0.32<br>0.31 | 0.37<br>0.33 | 0.01  | 0.033                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER | ENCES | EUROPEAN   | ISSUE DATE                      |

|----------|-----|-------|-------|------------|---------------------------------|

| VERSION  | IEC | JEDEC | EIAJ  | PROJECTION | ISSUE DATE                      |

| SOT102-1 |     |       |       |            | <del>93-10-14</del><br>95-01-23 |

### PAL/NTSC/SECAM synchronization processor for video recorders

TDA3755

#### **SOLDERING**

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (T<sub>stg max</sub>). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

### Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

### **DEFINITIONS**

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

| Limiting values           |                                                                                       |

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.