CA3089

FM IF System

OBSOLETE PRODUCT NO RECOMMENDED REPLACEMENT

FN561 Rev 4.00 October 2002

## Description

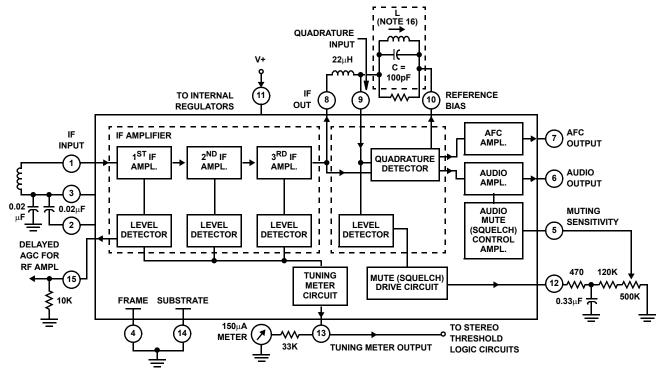

Intersil CA3089 is a monolithic integrated circuit that provides all the functions of a comprehensive FM-IF system. The block diagram shows the CA3089 features, which include a three-stage FM-IF amplifier/limiter configuration with level detectors for each stage, a doubly-balanced quadrature FM detector and an audio amplifier that features the optional use of a muting (squelch) circuit.

The advanced circuit design of the IF system includes desirable deluxe features such as delayed AGC for the RF tuner, and AFC drive circuit, and an output signal to drive a tuning meter and/or provide stereo switching logic. In addition, internal power supply regulators maintain a nearly constant current drain over the voltage supply range of +8.5V to +16V.

The CA3089 is ideal for high-fidelity operation. Distortion in a CA3089 FM-IF System is primarily a function of the phase linearity characteristic of the outboard detector coil.

#### Part Number Information

| PART<br>NUMBER      | TEMP. RANGE<br>(°C) | PACKAGE    | PKG. NO. |

|---------------------|---------------------|------------|----------|

| CA3089E             | -40 to 85           | 16 Ld PDIP | E16.3    |

| CA3089M1<br>(3089M) | -40 to 85           | 20 Ld SOIC | M20.3    |

#### **Features**

- For FM IF Amplifier Applications in High-Fidelity, Automotive, and Communications Receivers

- Includes: IF Amplifier, Quadrature Detector, AF Preamplifier, and Specific Circuits for AGC, AFC, Muting (Squelch), and Tuning Meter

- Low Distortion: (with Double-Tuned Coil) . . . . . . . . . . 0.1% (Typ)

- · Single-Coil Tuning Capability

- High Recovered Audio . . . . . . . . . . . . . . . 400mV (Typ)

- Provides Specific Signal for Control of Interchannel Muting (Squelch)

- Provides Specific Signal for Direct Drive of a Tuning Meter

- Provides Delayed AGC Voltage for RF Amplifier

- · Provides a Specific Circuit for Flexible AFC

- Internal Supply-Voltage Regulators

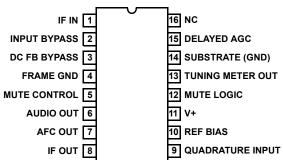

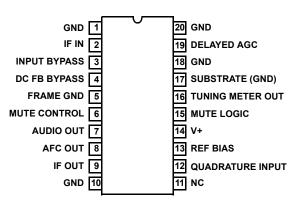

#### **Pinouts**

CA3089 (PDIP) TOP VIEW

CA3089 (SOIC) TOP VIEW

#### **Thermal Information Absolute Maximum Ratings** $\theta_{JA}$ (°C/W) Supply Voltage Thermal Resistance (Typical, Note 1) Between V+ and Frame GND ......16V PDIP Package..... SOIC Package..... DC Current (Out of Delayed AGC)......2mA Maximum Junction Temperature (Plastic Package) ......150°C Maximum Storage Temperature Range . . . . . . -65°C to 150°C **Operating Conditions** Maximum Lead Temperature (Soldering 10s) ............ 300°C Temperature Range.....-40°C to 85°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

(SOIC - Lead Tips Only)

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

### **Electrical Specifications** V+ = 12V (See Figures 3 and 4)

| (NOTE 3) PARAMETER                                        |                                 | TEST CONDITIONS                          |                                                                                                                           | TEMP.<br>(°C) | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------|---------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|-----|-------|

| DC CHARACTE                                               | RISTICS                         |                                          |                                                                                                                           |               |     |     |     |       |

| Quiescent Circuit Current                                 |                                 | No signal input, Non muted               |                                                                                                                           | 25            | 16  | 23  | 30  | mA    |

| DC Voltages Terminal 1 (IF Input)                         |                                 |                                          |                                                                                                                           |               | 1.2 | 1.9 | 2.4 | V     |

|                                                           | Terminal 2 (AC Return to Input) |                                          |                                                                                                                           |               | 1.2 | 1.9 | 2.4 | V     |

|                                                           | Terminal 3 (DC Bias to Input)   |                                          |                                                                                                                           |               | 1.2 | 1.9 | 2.4 | V     |

|                                                           | Terminal 6 (Audio Output)       | 7                                        |                                                                                                                           | 25            | 5.0 | 5.6 | 6.0 | V     |

|                                                           | Terminal 10 (DC Reference)      |                                          |                                                                                                                           | 25            | 5.0 | 5.6 | 6.0 | V     |

| DYNAMIC CHAP                                              | RACTERISTICS                    |                                          |                                                                                                                           |               |     |     |     |       |

| Input Limiting Voltage (-3dB point), V <sub>1</sub> (lim) |                                 | -                                        | $\begin{split} f_O &= 10.7 \text{MHz}, \\ f_{MOD} &= 400 \text{Hz}, \\ \text{Deviation} &= \pm 75 \text{kHz} \end{split}$ | 25            | -   | 12  | 25  | μV    |

| AM Rejection (Terminal 6), AMR                            |                                 | V <sub>IN</sub> = 0.1V,<br>AM Mod. = 30% |                                                                                                                           | 25            | 45  | 55  | -   | dB    |

| Recovered AF Voltage (Terminal 6) V <sub>O</sub> (AF)     |                                 | $V_{IN} = 0.1V$                          | 1                                                                                                                         | 25            | 300 | 400 | 500 | mV    |

| Total Harmonic<br>Distortion, THD<br>(Note 2)             | Single Tuned (Terminal 6)       |                                          |                                                                                                                           | 25            | -   | 0.5 | 1.0 | %     |

|                                                           | Double Tuned (Terminal 6)       |                                          |                                                                                                                           | 25            | -   | 0.1 | -   | %     |

| Signal Plus Noise to Noise Ratio (Terminal 6)             |                                 |                                          |                                                                                                                           | 25            | 60  | 67  | -   | dB    |

### NOTES:

- 2. THD characteristics are essentially a function of the phase characteristics of the network connected between Terminals 8, 9, and 10.

- 3. Terminal numbers refer to 16 Lead PDIP.

## Application Information

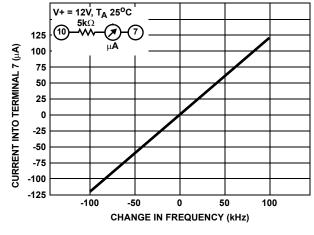

FIGURE 1. AFC CHARACTERISTICS (CURRENT AT TERMINAL 7) vs CHANGE IN FREQUENCY. (SEE **TEST CIRCUIT FIGURE 3)**

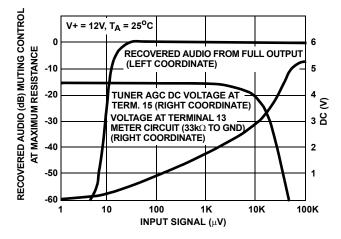

FIGURE 2. MUTING ACTION, TUNER AGC, AND TUNING METER OUTPUT vs INPUT SIGNAL VOLTAGE. (SEE TEST CIRCUIT FIGURE 3)

## **Test Circuits**

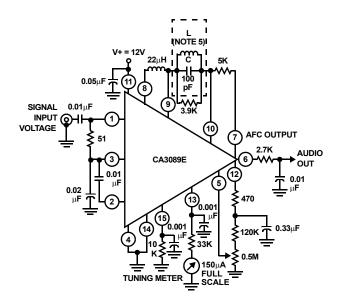

#### NOTES:

- 4. All resistance values are in ohms.

- 5. L tunes with 100pF (C) at 10.7MHz.

- 6.  $Q_0$  (unloaded)  $\cong$  75 (G.I. Automatic Mfg. Div. EX22741 or equivalent)

FIGURE 3. TEST CIRCUIT FOR CA3089E USING A SINGLE-TUNED DETECTOR COIL

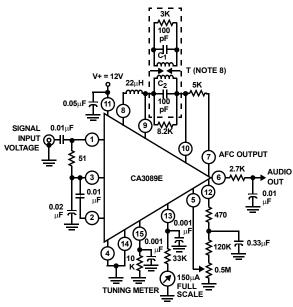

#### NOTES:

- 7. All resistance values are in ohms.

- 8. T PRI. Q0 (unloaded)  $\cong$  75 (tunes with 100pF (C1) 20 $\uparrow$  of 34e on  $^{7}/_{32}$ " dia. form).

- 9. SEC. Q0 (unloaded)  $\cong$  75 (tunes with 100pF (C2) 201 of 34e on  $^{7}/_{32}$  dia. form).

- 10. kQ (percent of critical coupling)  $\cong$  70%. (Adjusted for coil voltage  $V_C$ ) = 150mV.

Above values permit proper operation of mute (squelch) circuit "E" type slugs, spacing 4mm.

#### FIGURE 4. TEST CIRCUIT FOR CA3089E USING A DOUBLE-TUNED DETECTOR COIL

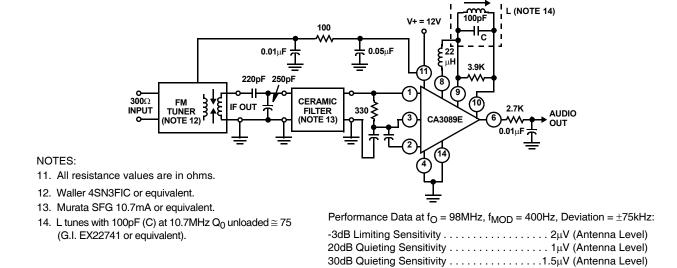

## **Test Applications**

FIGURE 5. TYPICAL FM TUNER USING THE CA3089E WITH A SINGLE TUNED DETECTOR COIL

## Test Applications (Continued)

FIGURE 6A. BOTTOM VIEW OF PRINTED CIRCUIT BOARD

FIGURE 6B. COMPONENT SIDE - TOP VIEW

FIGURE 6. ACTUAL SIZE PHOTOGRAPHS OF THE CA3089E AND OUTBOARD COMPONENTS MOUNTED ON A PRINTED-CIRCUIT BOARD

## **Block Diagram**

#### NOTES:

- 15. All resistance values are in ohms.

- 16. L Tunes with 100pF (C) at 10.7MHz.

- 17. QO @ 75 (G.I. EX22741 or equivalent).

- 18. Pin numbers refer to 16 lead DIP.

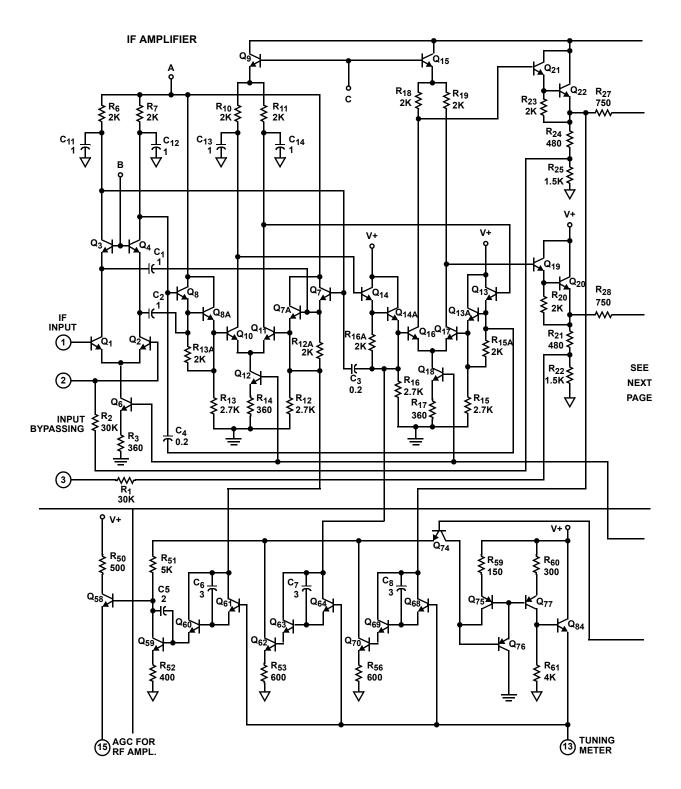

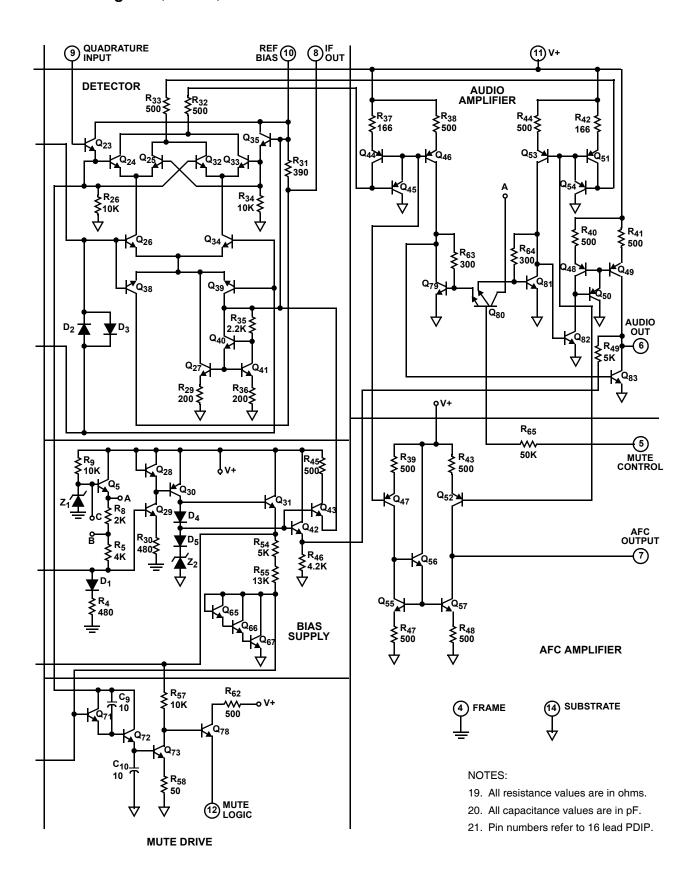

# Schematic Diagram

NOTE: Pin numbers refer to 16 lead PDIP.

LEVEL DETECTOR AND METER CIRCUIT

## Schematic Diagram (Continued)

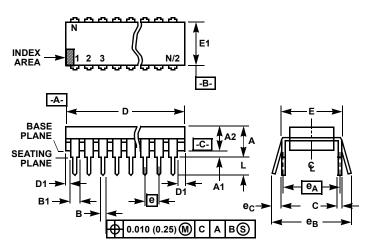

# Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- Dimensions A, A1 and L are measured with the package seated in JE-DEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E16.3 (JEDEC MS-001-BB ISSUE D)

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES |       | MILLIM   |       |       |  |

|----------------|--------|-------|----------|-------|-------|--|

| SYMBOL         | MIN    | MAX   | MIN      | MAX   | NOTES |  |

| Α              | -      | 0.210 | -        | 5.33  | 4     |  |

| A1             | 0.015  | -     | 0.39     | -     | 4     |  |

| A2             | 0.115  | 0.195 | 2.93     | 4.95  | -     |  |

| В              | 0.014  | 0.022 | 0.356    | 0.558 | -     |  |

| B1             | 0.045  | 0.070 | 1.15     | 1.77  | 8, 10 |  |

| С              | 0.008  | 0.014 | 0.204    | 0.355 | -     |  |

| D              | 0.735  | 0.775 | 18.66    | 19.68 | 5     |  |

| D1             | 0.005  | -     | 0.13     | -     | 5     |  |

| E              | 0.300  | 0.325 | 7.62     | 8.25  | 6     |  |

| E1             | 0.240  | 0.280 | 6.10     | 7.11  | 5     |  |

| е              | 0.100  | BSC   | 2.54 BSC |       | -     |  |

| e <sub>A</sub> | 0.300  | BSC   | 7.62 BSC |       | 6     |  |

| e <sub>B</sub> | -      | 0.430 | -        | 10.92 | 7     |  |

| L              | 0.115  | 0.150 | 2.93     | 3.81  | 4     |  |

| N              | 16     |       | 16       |       | 9     |  |

Rev. 0 12/93

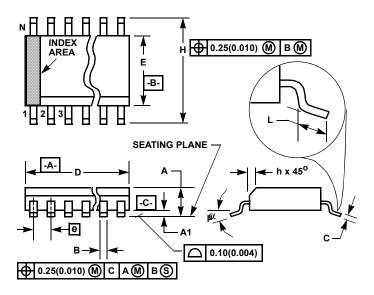

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M20.3 (JEDEC MS-013-AC ISSUE C)

20 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES    |        | MILLIN   |       |       |  |

|--------|-----------|--------|----------|-------|-------|--|

| SYMBOL | MIN       | MAX    | MIN      | MAX   | NOTES |  |

| Α      | 0.0926    | 0.1043 | 2.35     | 2.65  | -     |  |

| A1     | 0.0040    | 0.0118 | 0.10     | 0.30  | -     |  |

| В      | 0.013     | 0.0200 | 0.33     | 0.51  | 9     |  |

| С      | 0.0091    | 0.0125 | 0.23     | 0.32  | -     |  |

| D      | 0.4961    | 0.5118 | 12.60    | 13.00 | 3     |  |

| Е      | 0.2914    | 0.2992 | 7.40     | 7.60  | 4     |  |

| е      | 0.050 BSC |        | 1.27 BSC |       | -     |  |

| Н      | 0.394     | 0.419  | 10.00    | 10.65 | -     |  |

| h      | 0.010     | 0.029  | 0.25     | 0.75  | 5     |  |

| L      | 0.016     | 0.050  | 0.40     | 1.27  | 6     |  |

| N      | 20        |        | 2        | 20    | 7     |  |

| α      | 0°        | 8º     | 0°       | 8°    | -     |  |

Rev. 0 12/93

© Copyright Intersil Americas LLC 2002. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>