# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

#### 32x32 BIT SERIAL ELECTRICALLY ERASABLE PROM

The MCM2802 is a 1K-bit serial Electrically Erasable PROM designed for applications requiring both non-volatile memory and in-system information updates. In digital tuning systems, it provides storage for up to 32 channels. It has external control of timing functions and serial format for data and address.

- Single 5V supply in Read mode

- Organised as 32 Words of 32 Bits

- 5V and 25V supply for Erase and Program

- In-System Program/Erase Capability

- 0-100 kHz clock rate

- Floating gate process

- Expandable to 16K-bit systems

- Word and Array erasable

- 100.000 Write/Erase Cycles

# MCM2802

# MOS

(N-CHANNEL, SILICON GATE)

$32 \times 32$  BIT ELECTRICALLY ERASABLE PROM

P SUFFIX

PLASTIC PACKAGE

CASE 646

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maxi-

## MCM2802

# ABSOLUTE MAXIMUM RATINGS (Voltages referred to VSS)

| Rating                      | Symbol | Min.  | Max. | Unit |

|-----------------------------|--------|-------|------|------|

| DC Supply Voltage           | VDD    | - 0.5 | 8    | Vdc  |

| Programming Voltage         | Vpp    | - 0.5 | 28   | Vdc  |

| Input Voltage               | VIN    | - 0.5 | 8    | Vdc  |

| VP Control Output           | VPC    | - 0.5 | 28   | Vdc  |

| Operating Temperature Range | TA     | 0     | 70   | °C   |

| Storage Temperature Range   | тsтg   | - 55  | 150  | °C   |

NOTE - Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

# SWITCHING CHARACTERISTICS (T<sub>A</sub> = 0... $70^{\circ}$ C, $V_{DD}$ = 5V ± 10%, $V_{PP}$ = 25V ± 1V)

| Pin | Symbol | Parameter                                           | Fig. No. | Min. | Max. | Unit |

|-----|--------|-----------------------------------------------------|----------|------|------|------|

|     | tER    | Erase time                                          |          | 100  |      | ms   |

|     | twr    | Write time                                          |          | 10   |      | ms   |

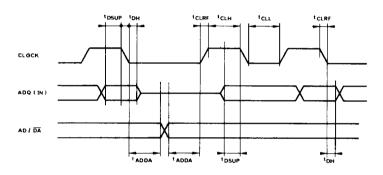

| CL  | FCL    | Clock Frequency F <sub>CL</sub> = 1/T <sub>CL</sub> | 2        |      | 100  | kHz  |

| CL  | tCLH   | Clock High Level Hold Time                          | 2        | 4    |      | μs   |

| CL  | tCLL   | Clock Low Level Hold Time                           | 2        | 4    |      | μs   |

| CL  | tCLRF  | Clock Fall Time and Rise Time                       | 2        |      | 1    | μS   |

|     | tAD/DA | Register Control to Clock                           |          |      |      |      |

|     |        | Delay Time except for tREAD                         | 2        | 1    |      | μs   |

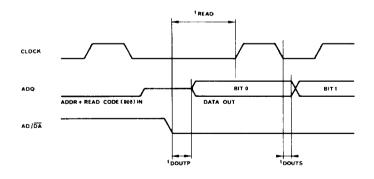

|     | tREAD. | After READ opcode only                              | 3        | 2    | 100  | μs   |

| ADQ | †DSUP  | Address/Data in Set-Up                              | 2, 3     | 2    |      | μs   |

|     | tDH    | Address/Data In Hold                                | 2, 3     | 2.0  |      | μs   |

| ADQ | tDOUTS | Data Out Serial Delay                               | 3        |      | 1    | μs.  |

|     | †DOUTP | Data Out Parallel Delay                             | 3        |      | 3    | μs   |

|     | Cout   | Output Capacitance (Vout = 0 V)                     |          |      | 12   | ρF   |

|     | Cin    | Input Capacitance (Vin = 0 V)                       |          |      | 12   | pF   |

DC CHARACTERISTICS (T<sub>A</sub> = 0...  $70^{\circ}$ C,  $V_{DD}$  = 5V ± 10%,  $V_{PP}$  = 25V ± 1V)

| Pin                      | Characteristic        | Condition       | Symbol | Min.  | Max. | Unit |

|--------------------------|-----------------------|-----------------|--------|-------|------|------|

| VPP                      | Supply Current        |                 | IPP    |       | 3    | mA   |

| $V_{DD}$                 | Supply Current        |                 | IDD    |       | 20   | mA   |

| ADQ                      | Tristate Input/Output | VOH = 2.4V      | ЮН     | - 0.1 |      | mA   |

|                          |                       | $V_{OL} = 0.5V$ | IOL :  | 1.6   |      | mA   |

|                          |                       | Tristate        | lin    |       | 10   | μА   |

| All Inputs<br>Except ADQ | Input Leakage         |                 | lin    |       | 10   | μА   |

| VPC                      | VP Control            | Von = 1V        | ION    | 0.7   |      | mA   |

|                          | Pull down device      | OFF state       | VMAX   |       | Vpp  | v    |

|                          |                       | VOFF = VP       | OFF    |       | 10   | μА   |

| All Inputs               | Input Low Voltage     | VIL             |        | 0.1   | 0.8  | v    |

|                          | Input High Voltage    | ViH             |        | 2.4   | 5.5  | v    |

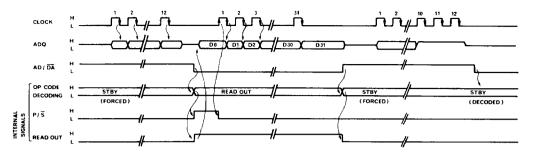

#### FIGURE 2 - GENERAL TIMINGS

FIGURE 3 - READOUT TIMINGS

## MCM2802

## FIGURE 4 - READOUT SEQUENCE

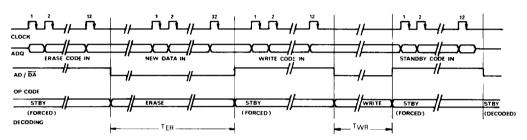

#### FIGURE 5 - WRITE SEQUENCE

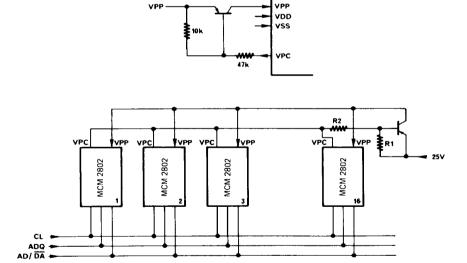

FIGURE 6 - VPP CONTROL AND MULTICHIP SETUP

#### MCM2802

#### **FUNCTIONAL DESCRIPTION**

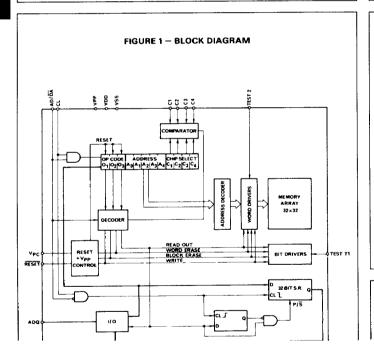

The circuit accepts 12 bits of Address/Op code in the address register and 32 bits of data in the data register (see figure 1; Block diagram).

## ADDRESS/OP CODE FORMAT (figure 1)

The four shifted bits C1 to C4 are used as chip select word in multichip systems. The chip address is defined by hardwiring the C1 to C4 pins. These bits are adjacent to the address field, so that no software modification is required in a program designed for a multi-1K memory application.

The five following A1 to A5 bits select one of the word addresses. The last 3 bits 01 to 03 control the operating modes

| Function    | 01 | 02 | 03 |

|-------------|----|----|----|

| Read        | 0  | 0  | 0  |

| Word Erase  | 0  | 1  | o  |

| Block Erase | 1  | 1  | 0  |

| Write       | 1  | О  | 0  |

| Standby     | ×  | x  | 1  |

# **READ OPERATION** (figure 4)

- The ADDRESS/OP CODE is loaded. The address selecting the word to be read and the op code bits being the READ code.

- 2) The AD/ $\overline{DA}$  is switched to the data mode, thus initiating the parallel transfer from the core to the shift register. First bit of data is present at the output.

- 3) As soon as the first of the 31 data out clock pulses is applied, the parallel transfer is stopped and data is shifted at the output. Data is recirculated in the data register.

- 4) The output buffer is turned on only when READ is internally decoded,  $AD/\overline{DA}$  is low and chip is selected by C1 and C4. Otherwise it is in the high impedance state. Addresses and data are clocked in and out with the falling edge of clock.

An erased bit corresponds to a low level output.

#### WRITING (figure 5)

- 1) ADDRESS/OP CODE is shifted in, the op code being either BLOCK ERASE or WORD ERASE.

- 2) Switching the AD/DAJine low fort = top a conditiates

- 4) The AD/ $\overline{DA}$  line is switched low again for a t = tWRITE, during which the selected word is programmed.

- 5) At the end of the WRITE operation it is recommended to load op code STANDBY and to return input  $AD/\overline{DA}$  to the low state.

#### ERASE

Both BLOCK ERASE and WORD ERASE are provided and are controlled by the op code. VPP has to be applied for BLOCK ERASE, WORD ERASE and for WRITE. For all other conditions it can be switched off to high impedance or VDD or VSS.

#### STANDBY

When AD/DA is high, the instruction decoder is disabled and hence STANDBY is forced. By shifting the STANDBY op code into the address register STANDBY will be recognized independently of the state of AD/DA.

#### CLOCK

The active high clock is only used for shifting data and addresses. This shift occurs on the clock falling edge.

#### **CHIP SELECTION**

The ADDRESS/DATA line can be used as a chip select in a system having other serial I/O devices. DATA and CLOCK lines being shared the non-volatile memory is only activated when the AD/DA line is low. Shifting information to the data register has no effect to the core while the chip is deselected.

In a multi-memory arrangement, all the lines including ADDRESS/DATA, CLOCK and DATA, are shared, with the exception of C1 to C4 which are hardwired to VDD or VSS, thus defining the circuit address. All Vp control outputs of the memory circuits can be combined in a wired OR configuration.

#### DATA PROTECTION

When Vpp is turned off, data stored in the array is always protected. A Vpp control output is provided for switching the Vpp supply. It consists of a pull down device to VSS. This device is turned on only when: VDD is present, a WRITE or ERASE code has been loaded in the address register and AD/ $\overline{\rm DA}$  is low.

Schematics for this external Vpp control are proposed in figure 6.

\_----