# DEVELOPMENT DATA

This data sheet contains advance information and specifications are subject to change without notice.

# 256 × 8-bit STATIC CMOS EEPROM WITH $I^2$ C-BUS INTERFACE

#### **GENERAL DESCRIPTION**

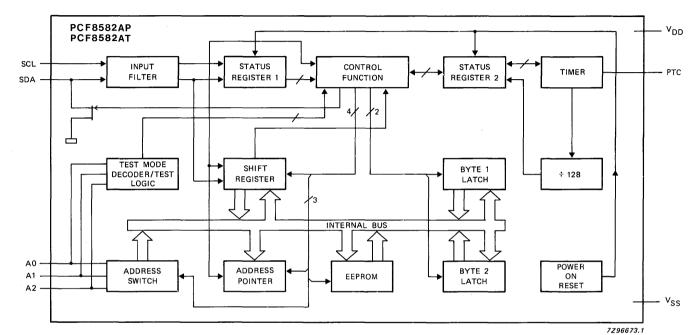

The PCF8582A is a 2 Kbits 5 Volt electrically erasable programmable read only memory (EEPROM) organized as 256 by 8-bits. It is designed in a floating gate CMOS technology.

As data bytes are received and transmitted via the serial I<sup>2</sup>C-bus, an eight pin DIL package is sufficient. Up to eight PCF8582A devices may be connected to the I<sup>2</sup>C-bus.

Chip select is accomplished by three address inputs.

Timing of the Erase/Write cycle can be done in two different ways; either by connecting an external clock to the "Programming Timing Control", pin (7 or 13), or by using an internal oscillator. If the latter is used an RC time constant must be connected to pin 7 or 13.

#### Features

- Non-volatile storage of 2 Kbits organized as 256 x 8

- Only one power supply required (5 V)

- On chip voltage multiplier for erase/write

- Serial input/output bus (I<sup>2</sup>C)

- Automatic word address incrementing

- Low power consumption

- One point erase/write timer

- Power on reset

- 10,000 erase/write cycles per byte

- 10 years non-volatile data retention

- Infinite number of read cycles

- Pin and address compatible to PCF8570, PCF8571, PCF8582 and PCD8572

- External clock signal possible.

A version with automotive temperature range -40 to  $+ 125 \text{ }^{\circ}\text{C}$  (PCF8582B) and a version with extended temperature range -40 to  $+ 85 \text{ }^{\circ}\text{C}$  (PCF8582C) are in preparation.

#### PACKAGE OUTLINE

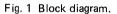

PCF8582AP; 8-lead dual in line; plastic (SOT97). PCF8582AT; 16-lead mini-pack; plastic (SO16L; SOT162A).

Z

482

May 1989

PCF8582A

PCF8582A

Fig. 2 (a) Pinning diagram.

| 23 | A1<br>A2 | address inputs/test<br>mode select |

|----|----------|------------------------------------|

| 4  | VSS      | ground                             |

| 5  | SDA (    | I <sup>2</sup> C-bus lines         |

| 6  | SCL∫     |                                    |

| 7  | РТС      | programming time control           |

| 8  | VDD      | positive supply                    |

|    |          |                                    |

|    |          |                                    |

|    |          |                                    |

|    |          |                                    |

|    |          |                                    |

address inputs/test

A0 1

1 n c

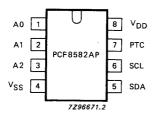

| 1  | n.c.            |                            |

|----|-----------------|----------------------------|

| 2  | n.c.            |                            |

| 3  | A0 )            |                            |

| 4  | A1 }            | address inputs/test        |

| 5  | A2 <sup>J</sup> | mode select                |

| 6  | VSS             | ground                     |

| 7  | n.c.            |                            |

| 8  | n.c.            |                            |

| 9  | n.c.            |                            |

| 10 | n.c.            |                            |

| 11 | SDA )           | 120 hun lines              |

| 12 | SCL )           | I <sup>2</sup> C-bus lines |

| 13 | PTC             | programming time control   |

| 14 | VDD             | positive supply            |

| 15 | n.c.            |                            |

| 16 | n.c.            |                            |

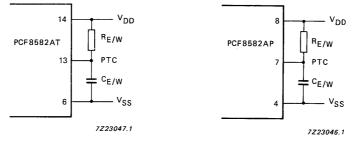

Figs. 3 (a) and (b) RC circuit connections to PCF8582AP and PCF8582AT when using the internal oscillator

May 1989

## FUNCTIONAL DESCRIPTION

# Characteristics of the l<sup>2</sup>C-bus

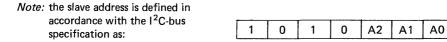

The I<sup>2</sup>C-bus is intended for communication between different ICs. The serial bus consists of two bi-directional lines, one for data signals (SDA), and one for clock signals (SCL). Both the SDA and the SCL lines must be connected to a positive supply voltage via a pull-up resistor.

The following protocol has been defined:

Data transfer may be initiated only when the bus is not busy.

During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as control signals.

The following bus conditions have been defined:

Bus not busy; both data and clock lines remain HIGH.

Start data transfer; a change in the state of the data line, from HIGH to LOW,

while the clock is HIGH defines the start condition. Stop data transfer; a change in the state of the data line, from LOW to HIGH, while the clock is HIGH, defines the stop condition.

Data valid; the state of the data line represents valid data when, after a start condition, the data line is stable for the duration of the HIGH period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a start condition and terminated with a stop condition; the number of the data bytes, transferred between the start and stop conditions is limited to two bytes in the ERASE/WRITE mode and unlimited in the READ mode. The information is transmitted in bytes and each receiver acknowledges with a ninth bit.

Within the  $I^2$ C-bus specifications a low speed mode (2 kHz clock rate) and a high speed mode (100 kHz clock rate) are defined. The PCF8582A operates in both modes.

By definition a device that sends a signal is called a "transmitter", and the device which receives the signal is called a "receiver". The device which controls the signal is called the "master". The devices that are controlled by the master are called "slaves".

Each word of eight bits is followed by one acknowledge bit. This acknowledge bit is a HIGH level put on the bus by the transmitter. The master generates an extra acknowledge related clock pulse. The slave receiver which is addressed is obliged to generate an acknowledge after the reception of each byte.

The master receiver must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter.

The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse in clock pulse.

Set-up and hold times must be taken into account. A master receiver must signal an end of data to the slave transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this condition the transmitter must leave the data line HIGH to enable the master generation of the stop condition.

#### Note

Detailed specifications of the I<sup>2</sup>C-bus are available on request.

May 1989

# I<sup>2</sup>C-Bus Protocol

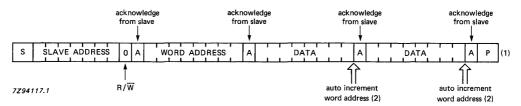

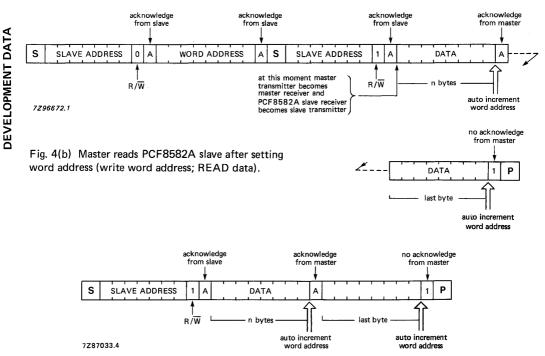

The  $I^2$ C-bus configurations for different READ and WRITE cycles of the PCF8582A are shown in Fig. 4, (a), (b) and (c).

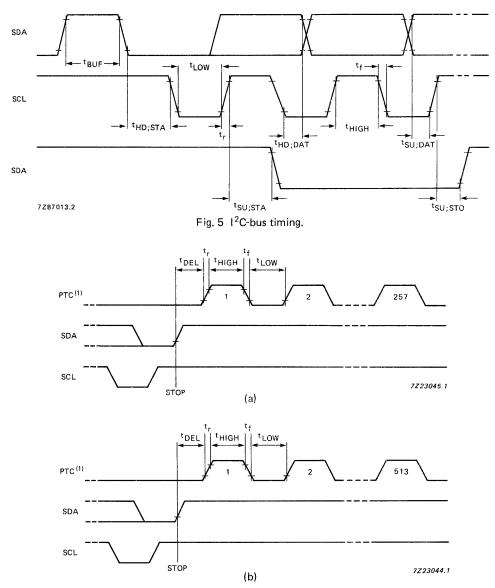

- (1) After this stop condition the erase/write cycle starts and the bus is free for another transmission. The duration of the erase/write cycle is approximately 30 ms if only one byte is written and 60 ms if two bytes are written. During the erase/write cycle the slave receiver does not send an acknowledge bit if addressed via the I<sup>2</sup>C-bus.

- (2) The second data byte is voluntary. It is not allowed to erase/write more than two types.

- Fig. 4(a) Master transmitter transmits to PCF8582A slave receiver (ERASE/WRITE mode).

Fig. 4(c) Master reads PCF8582A slave immediately after first byte (READ mode).\*

\* The device can be used as read only without the programming clock.

R/Ŵ

I<sup>2</sup>C-bus timing

(1) If external clock for PTC is chosen, this information is latched internally by leaving pin 7 LOW after transmission of the eight bit of the word address (negative edge of SCL). The state of PTC then, may be previously undefined.

Fig. 6 (a) One-byte ERASE/WRITE cycle; (b) two-byte ERASE/WRITE cycle.

486

# Ratings

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                                             | symbol           | min.                  | max.                  | unit |

|-------------------------------------------------------|------------------|-----------------------|-----------------------|------|

| Supply voltage                                        | VDD              | -0.3                  | +7                    | v    |

| Voltage on any input pin input impedance 500 $\Omega$ | VI               | V <sub>SS</sub> – 0.8 | V <sub>DD</sub> + 0.8 | v    |

| Operating temperature range                           | Tamb             | -40                   | +85                   | °C   |

| Storage temperature range                             | T <sub>stg</sub> | 65                    | +150                  | °C   |

| Current into any input pin                            | 11               | _                     | 1                     | mA   |

| Output current                                        | llol             | -                     | 10                    | mA   |

Purchase of Philips'  $l^2C$  components conveys a license under the Philips'  $l^2C$  patent to use the components in the  $l^2C$ -system provided the system conforms to the  $l^2C$  specifications defined by Philips.

$\mathbf{r}^{*}$

# CHARACTERISTICS

$V_{DD}$  = 5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 to +85  $^{\rm o}C$ ; unless otherwise specified.

| parameter                                                         | conditions                                         | symbol           | min.                       | typ. | max.                      | unit   |

|-------------------------------------------------------------------|----------------------------------------------------|------------------|----------------------------|------|---------------------------|--------|

| Operating supply voltage                                          |                                                    | V <sub>DD</sub>  | 4.5                        | 5.0  | 5.5                       | v      |

| Operating supply<br>current READ                                  | V <sub>DD</sub> max.<br>f <sub>SCL</sub> = 100 kHz | IDD              | _                          | _    | 0.4                       | mA     |

| Operating supply<br>current<br>WRITE/ERASE                        | V <sub>DD</sub> max.                               | <sup>I</sup> DDW | _                          | _    | 2.0                       | mA     |

| Standby supply current                                            | V <sub>DD</sub> max.                               | 1 <sub>DDO</sub> | -                          | -    | 10                        | μA     |

| Input PTC                                                         |                                                    |                  |                            |      |                           |        |

| Input voltage HIGH<br>Input voltage LOW                           |                                                    |                  | V <sub>DD</sub> – 0.3<br>– | _    | <br>V <sub>SS</sub> + 0.3 | V<br>V |

| Input SCL and input/output SDA                                    |                                                    |                  |                            |      |                           |        |

| Input voltage LOW                                                 |                                                    | VIL              | -0.3                       |      | 1.5                       | v      |

| Input voltage HIGH                                                |                                                    | VIH              | 3.0                        | _    | V <sub>DD</sub> + 0.8     | V      |

| Output voltage LOW                                                | I <sub>OL</sub> = 3 mA<br>V <sub>DD</sub> = 4.5 V  | VOL              |                            | -    | 0.4                       | v      |

| Output leakage<br>current HIGH                                    | V <sub>OH</sub> = V <sub>DD</sub>                  | LO               | _                          | —    | 1                         | μA     |

| Input leakage<br>current (SCL)                                    | VI = VDD or VSS                                    | LI               | _                          | -    | 1                         | μA     |

| Clock frequency                                                   |                                                    | <sup>f</sup> SCL | 0                          | —    | 100                       | kHz    |

| Input capacitance<br>(SCL; SDA)                                   |                                                    | CI               | _                          | -    | 7                         | pF     |

| Time the bus must be<br>free before new<br>transmission can start |                                                    | <sup>t</sup> BUF | 4.7                        | _    | _                         | μs     |

| Start condition hold<br>time after which first<br>clock pulse is  |                                                    | <b>-</b>         |                            |      |                           |        |

| generated                                                         |                                                    | THD;STA          | 4                          | -    | -                         | μs     |

| parameter                                                        | conditions                                                    | symbol                                                                                      | min.                        | typ. | max.                 | unit                        |

|------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------|------|----------------------|-----------------------------|

| The LOW period<br>of the clock                                   |                                                               | tLOW                                                                                        | 4.7                         | _    | _                    | μs                          |

| The HIGH period<br>of the clock                                  |                                                               | thigh                                                                                       | 4.0                         | _    | _                    | μs                          |

| Set-up time for<br>start condition                               | repeated start only                                           | <sup>t</sup> SU;STA                                                                         | 4.7                         |      | _                    | μs                          |

| Data hold time for I <sup>2</sup> C-<br>bus compatible masters   |                                                               | <sup>t</sup> HD;DAT                                                                         | 5.0                         | -    | _                    | μs                          |

| Data hold time for I <sup>2</sup> C devices                      | note 1                                                        | <sup>t</sup> HD;DAT                                                                         | 0                           | _    | _                    | ns                          |

| Date set up time                                                 |                                                               | <sup>t</sup> SU; DAT                                                                        | 250                         | _    | _                    | ns                          |

| Rise time for SDA<br>and SCL lines                               |                                                               | t <sub>r</sub>                                                                              |                             | -    | 1                    | μs                          |

| Fall time for SDA<br>and SCL lines                               |                                                               | t <sub>f</sub>                                                                              | _                           | _    | 300                  | ns                          |

| Set-up time for stop condition                                   |                                                               | T <sub>SU;STO</sub>                                                                         | 4.7                         | _    |                      | μs                          |

| Programming time control                                         |                                                               |                                                                                             |                             |      |                      |                             |

| Erase/write cycle time                                           |                                                               | <sup>t</sup> E/W                                                                            | 5                           | -    | 40                   | ms                          |

| Capacitor used for E/W<br>cycle of 30 ms                         | max. tolerance ±10%;<br>using internal<br>oscillator (Fig. 3) | C <sub>E/W</sub>                                                                            |                             | 3.3  |                      | nF                          |

| Resistor used for E/W cycle of 30 ms                             | max. tolerance ±5%;                                           | L/ VV                                                                                       |                             |      |                      |                             |

|                                                                  | using internal<br>oscillator (Fig. 3)                         | R <sub>E/W</sub>                                                                            | -                           | 56.0 | _                    | kΩ                          |

| Programming<br>frequency using<br>external clock                 |                                                               |                                                                                             |                             |      |                      |                             |

| Frequency<br>Period LOW<br>Period HIGH<br>Rise-time<br>Fall-time |                                                               | <sup>f</sup> p<br><sup>t</sup> LOW<br><sup>t</sup> HIGH<br>t <sub>r</sub><br>t <sub>f</sub> | 10<br>10.0<br>10.0<br><br>- |      | 50<br><br>300<br>300 | kHz<br>μs<br>μs<br>ns<br>ns |

| Delay-time<br>Data retention time                                | T <sub>amb</sub> = 55 <sup>o</sup> C                          | <sup>t</sup> d<br>tS                                                                        | 0<br>10                     | -    | _                    | ns<br>years                 |

# Note to the characteristics

1. The hold time required to bridge the undefined region of the falling edge of SCL must be internally provided by a transmitter. It is not greater than 300 ns.

## CHARACTERISTICS (continued)

#### E/W programming time control

A. Using external resistor  $R_{E/W}$  and capacitor  $C_{E/W}$  (see Table 1)

Table 1

Recommended R, C combinations

| R <sub>E/W</sub><br>(kΩ)<br>note 1 | C <sub>E/W</sub><br>(nF)<br>note 2 | t <sub>E/W</sub> (typ.)<br>(ms)<br>note 3 |

|------------------------------------|------------------------------------|-------------------------------------------|

| 56                                 | 3.3                                | 34                                        |

| 56                                 | 2.2                                | 21                                        |

| 22                                 | 3.3                                | 13                                        |

| 22                                 | 2.2                                | 7.5 (note 4)                              |

#### Notes to Table 1

- 1. Maximum tolerance is 10%.

- 2. Maximum tolerance is 5%.

- 3. Actual E/W lines are mainly influenced by the tolerances in values of R and C.

- 4. Minimum allowed  $t_{E/W}$  is 5 ms (see CHARACTERISTICS).

#### B. Using an external clock (see Table 2 and Fig.6)

| párameters  | symbol         | min. | max. | unit |

|-------------|----------------|------|------|------|

| frequency   | fp             | 10.0 | 50.0 | kHz  |

| period LOW  | tLOW           | 10.0 | _    | S    |

| period HIGH | thigh          | 10.0 |      | s    |

| rise time   | tr             | _    | 300  | ns   |

| fall time   | t <sub>f</sub> | -    | 300  | ns   |

| delay time  | t <sub>d</sub> | 0    | -    | ns   |

Table 2 E/W programming time control using an external clock

490