## 54/74LS301 (O.C.)

# 256-BIT TTL RAM (256 $\times$ 1)

### DESCRIPTION

The 54/74LS301 is a Read/Write memory array which features an open collector output for optimization of word expansion in bused organizations. Memory expansion is further enhanced by full on-chip address decoding, 3 chip enable inputs and PNP input transistors, which reduce input loading.

The additional feature of output blanking during Write (Do terminal "H") permits Do and DIN terminals to share a common I/O line to reduce system interconnections. These devices have fast Read access and Write cycle times, and thus are ideally suited in high-speed memory applications such as cache, buffers, scratch pads, writable control stores, etc.

The 54/74LS301 is available in both the commercial temperature range (0°C to

+ 75°C) and the military temperature range (-55°C to +125°C). They are specified as: N74LS301F or N for the commercial temperature range, and S54LS301F, G, or W for the military temperature range. Military products are available as fully processed to Mil-Std 883 Level B or Level C; specify either 883B or 883C.

See page 4-9 for Truth Table, Timing Diagrams, Test Circuit and Waveform.

### **FEATURES**

- · Address access time: N74LS301: 40ns max S54LS301: 70ns max

- · Write cycle time:

N74LS301: 25ns max S54LS301: 60ns max

- . Power dissipation: 0.98mW/bit typ

- · Input loading:

N74LS301: - 100µA max S54LS301: - 250µA max

- . Output blanking during Write

- · On-chip address decoding

- · Schottky clamped

- TTL compatible

#### **APPLICATIONS**

- · Buffer memory

- Memory mapping

- · Scratch pad

- Writable control store

- Push down stack

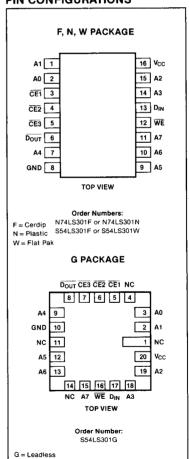

### PIN CONFIGURATIONS

### **ABSOLUTE MAXIMUM RATINGS**

|                  | PARAMETER                       | RATING                         | UNIT       |

|------------------|---------------------------------|--------------------------------|------------|

| V <sub>CC</sub>  | Supply voltage                  | + 7                            | Vdc        |

| VIN              | Input voltage<br>Output voltage | + 5.5                          | Vdc<br>Vdc |

| $V_{OUT}$        | High (open collector)           | + 5.5                          |            |

| TA               | Temperature Range<br>Operating  |                                | °C         |

|                  | N grade                         | 0 to +70                       |            |

| T <sub>STG</sub> | S grade<br>Storage              | - 55 to + 125<br>- 65 to + 150 | °C         |

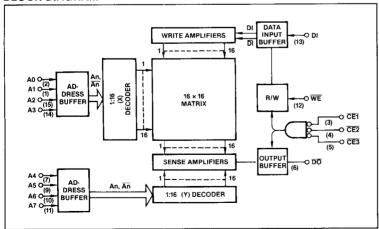

### **BLOCK DIAGRAM**

# 256-BIT TTL RAM (256×1)

# 54/74LS301 (O.C.)

DC ELECTRICAL CHARACTERISTICS N74LS301:  $0^{\circ}C \le T_{A} \le + 75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$ \$54LS301:  $-55^{\circ}C \le T_{A} \le + 125^{\circ}C$ ,  $4.5V \le V_{CC} \le 5.5V$

| PARAMETER                                             |                                                                 |                                                              | N74LS301 |                  |               | S54LS301 |                  |              | T    |

|-------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|----------|------------------|---------------|----------|------------------|--------------|------|

|                                                       |                                                                 | TEST CONDITIONS                                              | Min      | Typ <sup>1</sup> | Max           | Min      | Typ <sup>1</sup> | Max          | UNIT |

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>IC</sub> | Input voltage <sup>2</sup><br>Low<br>High<br>Clamp <sup>3</sup> | $V_{CC} = min$ $V_{CC} = max$ $V_{CC} = min, I_{IN} = -18mA$ | 2.0      |                  | 0.85<br>- 1.2 | 2.0      |                  | 0.8<br>- 1.2 | V    |

| VoL                                                   | Output voltage<br>Low <sup>5</sup>                              | $V_{CC} = min$ $I_{OL} = 16mA$                               |          |                  | 0.45          |          |                  | 0.50         | V    |

| իլ<br>հո                                              | Input current <sup>2</sup><br>Low<br>High                       | $V_{CC} = max$ $V_{IL} = 0.45V$ $V_{IH} = 2.7V$              |          |                  | ~ 100<br>25   |          |                  | - 250<br>25  | μΑ   |

| lock                                                  | Output current<br>Leakage <sup>5</sup>                          | $V_{1H} = 2V, V_{O} = 5.5V$                                  |          |                  | 40            |          |                  | 50           | μΑ   |

| lcc                                                   | V <sub>CC</sub> supply current <sup>8</sup>                     | V <sub>CC</sub> = max                                        |          | 50               | 70            |          | 50               | 100          | mA   |

| C <sub>IN</sub><br>C <sub>OUT</sub>                   | Capacitance<br>Input<br>Output                                  | $V_{CC} = 5.0V$ $V_{1N} = 2.0V$ $V_{OUT} = 2.0V$             |          | 5<br>8           |               |          | 5<br>8           |              | pF   |

### AC ELECTRICAL CHARACTERISTICS $R1 = 270\Omega, R2 = 1K\Omega, C_L = 15pF$

N74LS301:  $0^{\circ}C \le T_A \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$ S54LS301:  $-55^{\circ}C \le T_A \le +125^{\circ}C$ ,  $4.5V \le V_{CC} \le 5.5V$

| PARAMETER                            |                                                |                  |                             | N       | N74LS301         |          |          | S54LS301         |          |          |

|--------------------------------------|------------------------------------------------|------------------|-----------------------------|---------|------------------|----------|----------|------------------|----------|----------|

|                                      |                                                | то               | FROM                        | Min     | Typ <sup>1</sup> | Max      | Min      | Typ <sup>1</sup> | Max      | UNIT     |

| T <sub>AA</sub><br>T <sub>CE</sub>   | Access time<br>Address<br>Chip enable          | Output<br>Output | Address<br>Chip enable      |         | 30<br>15         | 40<br>25 |          | 30<br>15         | 70<br>40 | ns       |

| T <sub>CD</sub><br>T <sub>WD</sub>   | Disable time<br>Valid time                     | Output<br>Output | Chip enable<br>Write enable |         | 15<br>30         | 25<br>40 |          | 15<br>30         | 40<br>55 | ns<br>ns |

| T <sub>WSA</sub><br>T <sub>WHA</sub> | Setup and hold time<br>Setup time<br>Hold time | Write enable     | Address                     | 0       | -5<br>-5         |          | 10<br>10 | - 5<br>- 5       | 1        | ns       |

| T <sub>WSD</sub><br>T <sub>WHD</sub> | Setup time<br>Hold time                        | Write enable     | Data in                     | 25<br>0 | 15<br>-5         |          | 40<br>10 | 15<br>-5         |          |          |

| T <sub>WSC</sub><br>T <sub>WHC</sub> | Setup time<br>Hold time                        | Write enable     | CE CE                       | 0       | - 5<br>- 5       |          | 10<br>10 | -5<br>-5         |          |          |

| T <sub>WP</sub>                      | Pulse width<br>Write enable <sup>9</sup>       |                  |                             | 25      | 15               |          | 40       | 15               | }        | ns       |

#### NOTES

- 1. All typical values are at  $V_{CC} = 5V$ ,  $T_A + 25$  °C.

- 2. All voltage values are with respect to network ground terminal.

- 3. Test each input one at a time.

- 4. Measured with a logic low stored and  $V_{1L}$  applied to  $\overline{\text{CE1}}$ ,  $\overline{\text{CE2}}$  and  $\overline{\text{CE3}}$ .

- 5. Measured with a logic high stored. Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 6. Measured with VIH applied to CE1, CE2 and CE3.

- 7. Duration of the short-circuit should not exceed 1 second.

- I<sub>CC</sub> is measured with the Write enable and memory enable inputs grounded, all other inputs at 4.5V, and the output open.

- 9. Minimum required to guarantee a Write into the slowest bit.

# 256-BIT TTL RAM (256×1)

### **TRUTH TABLE**

|           |     |    |                 | D <sub>OUT</sub>      |                |                              |  |

|-----------|-----|----|-----------------|-----------------------|----------------|------------------------------|--|

| MODE      | CE* | WE | D <sub>IN</sub> | 54/74S301, 54/74LS301 | 82S16/LS16     | 82S17/LS17<br>Stored<br>data |  |

| Read      | 0   | 1  | Х               | Stored<br>data        | Stored<br>data |                              |  |

| Write "0" | 0   | 0  | 0               | 1                     | 1 1            | 1                            |  |

| Write "1" | 0   | 0  | 1               | 1                     | 0              | 0                            |  |

| Disabled  | 1   | х  | ×               | 1 Hi-Z                |                | 1                            |  |

<sup>\*&</sup>quot;0" = All CE inputs low; "1" = One or more CE inputs high.

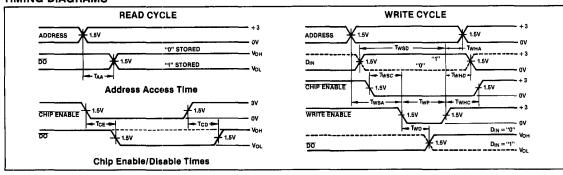

### **TIMING DIAGRAMS**

### **MEMORY TIMING DEFINITIONS**

Delay between beginning of chip TCE enable low (with address valid) and when data output becomes valid.

TCD Delay between when chip enable becomes high and data output is in off state.

$T_{\text{AA}}$ Delay between beginning of valid address (with chip enable low) and when data output becomes valid.

Twsc Required delay between beginning of valid chip enable and beginning of Write enable pulse.

Required delay between end of TWHD Write enable pulse and end of valid input data.

Width of Write enable pulse. TWP TWSA

Twsp

Required delay between beginning of valid address and beginning of Write enable pulse.

Required delay between beginning of valid data input and end of Write enable pulse.

$T_{WD}$

Twhc

Delay between beginning of Write enable pulse and when data output reflects complement of data input.

Required delay between end of Write enable pulse and end of chip enable.

$T_{WHA}$ Required delay between end of

Write enable pulse and end of valid address.

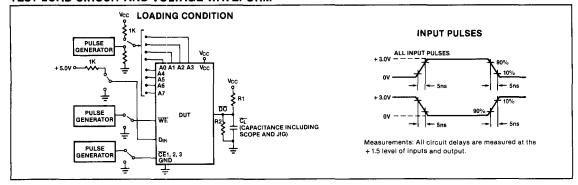

### TEST LOAD CIRCUIT AND VOLTAGE WAVEFORM

X = Don't care.